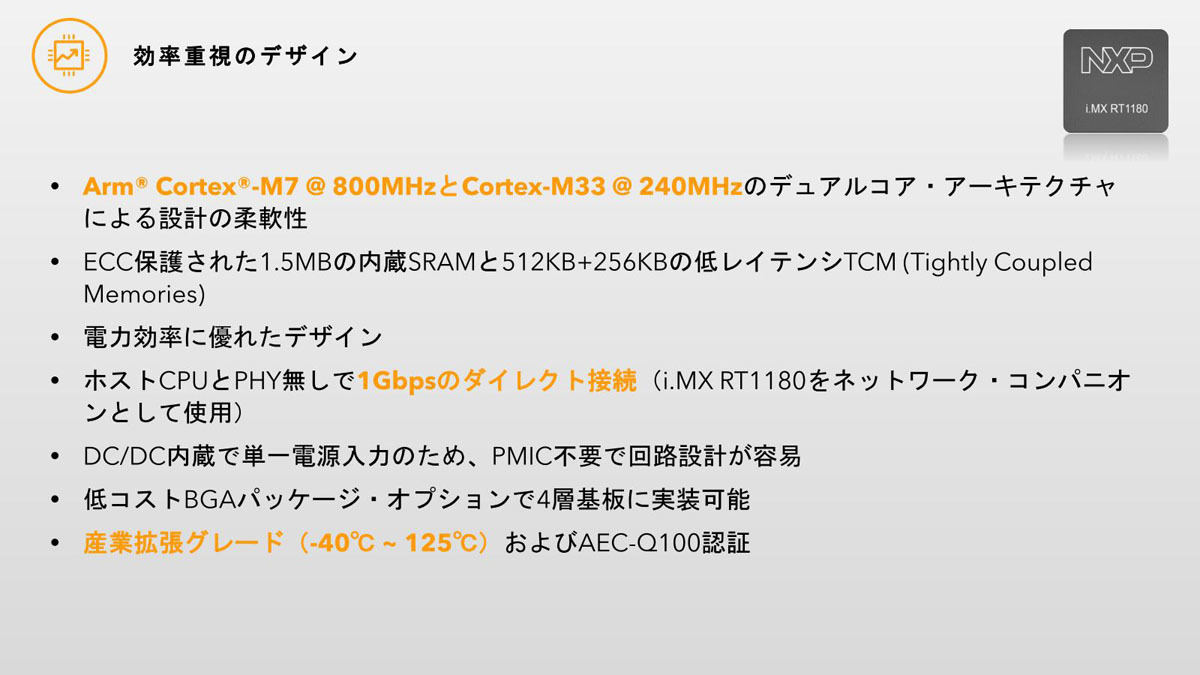

プロセッサ構成という意味では、800MHzのCortex-M7+240MHz Cortex-M33に1.5MB SRAMと384KB TCMの構成でややi.MX RT1170に見劣りする(i.MX RT 1170は1GHz Cortex-M7+400MHz Cortex-M4に2MB SRAM+512KB TCMの構成)のだが、多分これに関しては逆にアプリケーション要件からこの辺りの性能で十分、というフィードバックがあったのではないかと思われる(Photo04)。

変わったところでは、ホストCPUとの独自Linkを用意しており、ホストCPUのEthernet PHY(というか、ネットワーク Companion)として動作できる点が特徴的である。

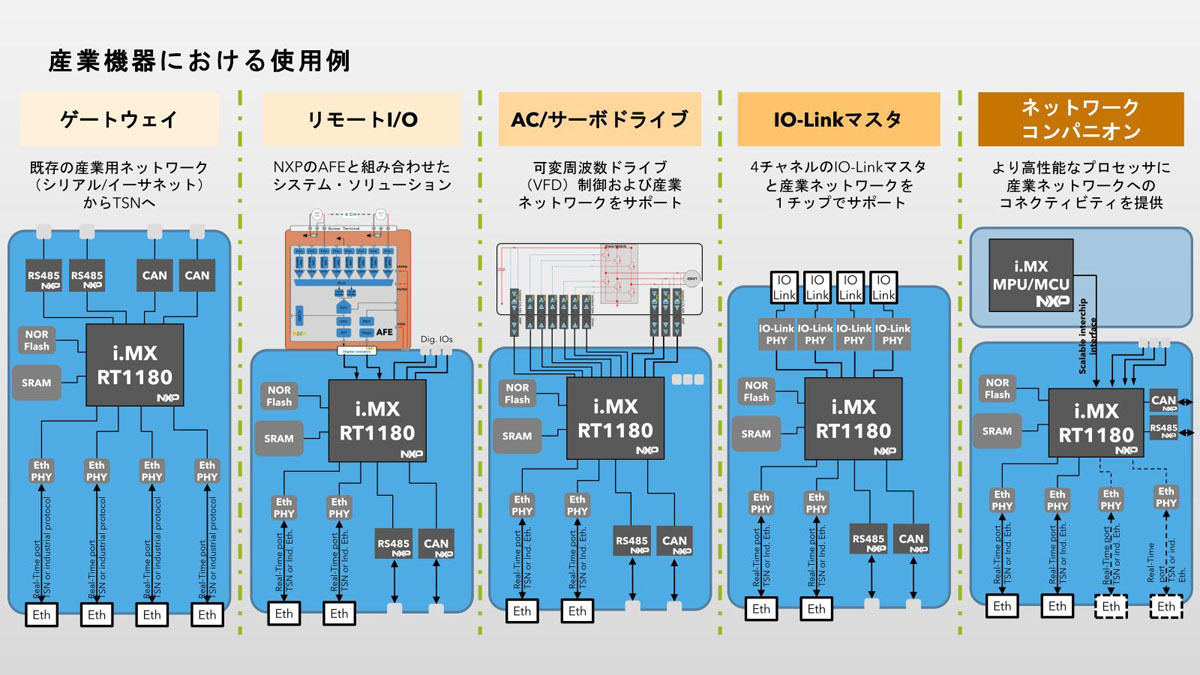

実際にi.MX RT1180を利用する例、というのがこちら(Photo05)。

-

Photo05:i.MX RT1180はEthernet/SwitchともにMACまでは統合され、PHYは別になっている。なので、後は用途に合わせてPHYを入れ替える事で複数のプロトコルに対応可能とされる

上で書いたホストCPUとの独自リンクの例が一番右端である。この際ホストとはRGMII、ないしFLEXSPIで接続されるという事だった。RGMIIであれば、既存のEthenetのPHYの代わりにi.MX RT1180を接続するだけで済む(ただこの場合i.MX RT1180はホストからはPHYとして見えるので、独自機能はi.MX RT1180側に実装する必要がある)。もう少しホストから細かく制御を行いたい、と言う場合はFLEXSPIで接続するという形になるのだろう。

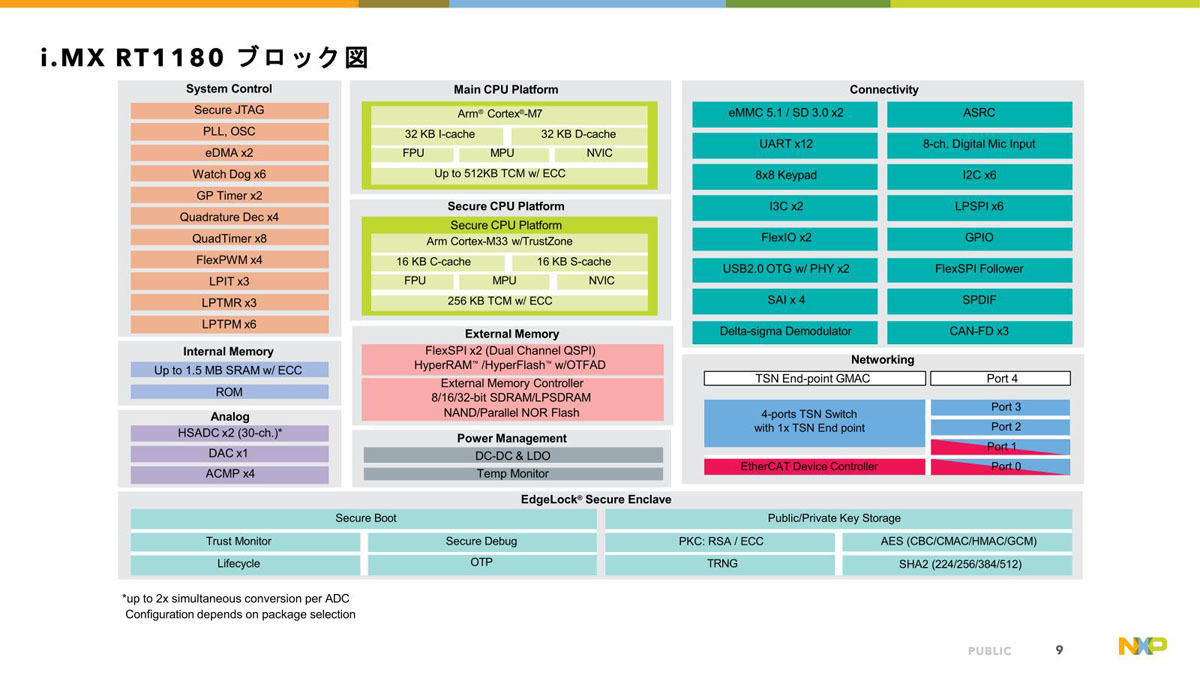

i.MX RT1180の構成はこんな感じ(Photo06)。周辺回路なども豊富なので、ネットワークコンパニオンいうかネットワークブリッジだけに使うにはややもったいない構成であるが、ただ逆に言えば同一のチップで複数の用途に使いまわせることがPhoto01で言う「効率重視のデザイン」にるながる事を考えれば、これも悪い事ではないだろう。

ちなみにi.MX RT1180は現時点ではPre-productionという段階である。同社によれば特定顧客へのサンプル開始は今年7月、General Samplingは今年末もしくは来年あたりということで、まだ決まっていない模様だ。