富士通は京コンピュータの開発を担当し、その技術を使ってPRIMEHPC FX10という商用スパコンを開発している。FX10は、すでに、東大の柏センター、東大物性研、名古屋大、台湾気象庁などに導入されている。

この次に、富士通がどのようなスパコンを出してくるのかという疑問に答えて、富士通はSC13においてベンダーフォーラムでHPCロードマップの発表を行ない、FX10後継機のプロトタイプをブースで展示していた。

ベンダーフォーラムでのHPCロードマップの発表

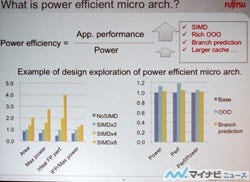

スパコンではLINPACK性能でランクするTop500やLINPACK/WでランキングするGreen500などが良く語られるが、本当に重要なのは実アプリ性能/Wである。富士通は、京コンピュータや後継のFX10での経験を使い、各種の実アプリについて、各種のアーキテクチャ的な強化を組み込むことによる性能や消費電力への影響をシミュレーションで求めた。その結果の一部が次の図に示されている。

SIMD演算の幅を1/2/4/8と増やすと、チップ面積、電力、性能ともに増加するが、性能/電力を取ると、SIMD数が大きいほうが有利で、FX10の2SIMDに比べて4SIMDでは20%、8SIMDでは40%程度エネルギー効率が向上する。

FX10のマイクロアーキテクチャをベースラインとし、O-o-O実行を強化すると、実アプリで性能が20%近く向上するだけでなく、エネルギー効率が5~6%向上する。また、分岐予測を強化すると、性能が5%程度向上し、エネルギー効率が2~3%向上するという。

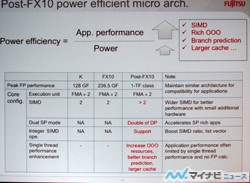

したがって、Post-FX10プロセサでは、FX10の2SIMDからSIMD幅の拡張、O-o-O実行リソースや分岐予測リソースを増加させ、キャシュメモリ量を増やす。これは、実アプリの中の並列化できずシングルスレッドで実行せざるを得ない部分の実行時間を短縮し、全体の実行時間を短縮すると言う点で重要であるという。

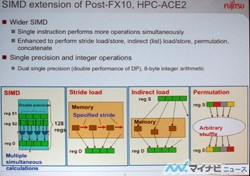

また、京やFX10のプロセサは64bitの倍精度浮動小数点の演算でも、32bitの単精度浮動小数点の演算でも同じ数しか実行できなかったが、Post-FX10プロセサでは、Intelのプロセサなどと同様に、単精度の場合は2演算を実行できるように変更する。従来、科学技術計算は倍精度が多かったが、Intelなどのプロセサは単精度なら2倍の演算ができるため、科学技術計算の中でも単精度で済む部分は単精度を使い、精度が不足する部分だけ倍精度を使うというような使い方が増加しており、富士通もこれに追従することにしたものである。

そして、SIMDの拡張として、次の図が示された。

|

|

この図では4並列のSIMD演算で、一定間隔のデータを読むStride Loadやアドレスアレイを使って飛び飛びに読むIndirect LoadとSIMDの4要素の順序を入れ替えるPermutationをサポートする計画 |

この図では4並列のSIMDの図になっており、Post-FX10は4SIMDの可能性が高いと思われるが、8SIMDだが図を簡単にするため4並列で描いたという可能性も排除できない。

SIMDの弱点は連続したメモリアドレスから並列データを読んでくることしかできないという点であるが、それを補うため、一定間隔のアドレスからデータを読むStrideアクセスと、アドレスを書いたレジスタに従って不連続なアドレスからデータを読むIndirectアクセスをサポートする。なお、この図ではLoadだけが書かれているが、この逆のStride Store、Indirect Storeもサポートされている。

そして、読み込んだデータをレジスタの中で順序を入れ替えるPermutation命令を追加する。これだけの機能が追加されれば、SIMDはかなり使いやすくなる。

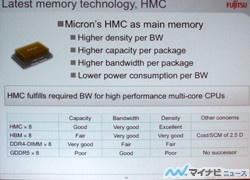

そして、Post-FX10の1つの目玉がMicronのHMC(Hybrid Memory Cube)の採用である。MicronのブースではHMCを採用したボードを数種類展示していたが、富士通のこのボード以外のボードは1個のHMCの搭載で、24個も搭載されているPost-FX10のボードは目を引く存在であった。

富士通は、HMCは容量ではDDR4-DIMMに劣るものの、バンド幅は非常に高く、実装密度が極めて高いことから、スパコンのメモリとしてはHMCが最適としている。

富士通はPost-FX10 CPUのメモリバンド幅は非公表としているが、清水氏の発表では、Byte/Flopsとして、京と同じ0.5を維持したいと述べており、CPUチップのFlopsが1TFlops以上と書かれていることと合わせると、メモリバンド幅は500GB/s以上ということになる。

HMCは高速シリアルリンクでデータ伝送を行い、近距離の伝送の場合は15Gbit/sで伝送する仕様となっている。そして1リンクは入出力それぞれ16本の信号線からなっている。したがって、入出力を合計すると、1リンクで60GB/sのメモリバンド幅を持っている。

MicronのHMCは31mm角のパッケージと16mm×19.5mmのパッケージのものがあり、大きいパッケージは4本のリンクを持つが、Post-FX10が採用する小さいパッケージのHMCは2リンクとなっている。

この2リンクをCPUチップに直結すると、8個のHMCの合計ではメモリバンド幅は960GB/sとなり500GB/s以上という要件に対しては大きすぎる感じもするが、HMCリンクには10Gbit/s、12.5Gbit/sという規格もあり、これらの伝送速度を使っている可能性もある。また、1TFlops以上という演算性能が、実は1TFlopsをかなり超えるという可能性も考えられる。

しかし、HMCの採用には懸念もある。大規模計算は大量の演算を必要とするだけでなく、大量のデータを格納するメモリ容量も必要とするものが多い。京コンピュータは、1Flopsの演算能力あたり0.125Byteのメインメモリを搭載している。しかし、HMCの容量は現在2GBで、来年には4GBという程度である。1TFlopsのCPUに32GBのメインメモリとすると、Flopsあたりのメインメモリ容量は0.03Byteと京コンピュータの1/4に留まる。

もう1つのHMCの懸念はコストである。この点について、SC13会場で、富士通の幹部に質問したところ「これからMicronと価格交渉」とのことであった。

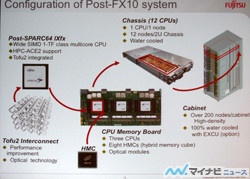

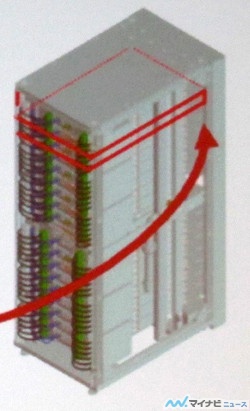

そして、CPUチップからキャビネットまでのシステム構成は次の図のようになる。

インタコネクトはTofu2と書かれており、京コンピュータで開発したTofuインタコネクトをベースにバンド幅やレイテンシの改善を行う。また、光伝送のサポートを追加するという。この資料からは、6次元のメッシュ/トーラスというトポロジについては変更がないと考えられる。なお、京コンピュータやFX10では、TofuインタコネクトにはICCという別チップを必要としていたが、Post-FX10のボードでは別チップは見えず、すべてCPUチップに集積されているようである。

Tofuはa、b、cの2×3×2のローカル次元で12ノードを接続し、この12ノードをグループとして、X、Y、Zのグローバル次元で3次元トーラス接続するというトポロジとなっている。

CPU Memoryボードに3CPU搭載というのは、中途半端な数のような感じがするが、b次元の3ノード分を1ボードに搭載したものである。そして、次の階層であるシャーシには4ボード、12ノードが搭載されており、a、b、cのローカル次元の12ノードのグループを構成すると考えられる。

この写真のキャビネットの部分を拡大したのが次の図である。

前の図では200ノード以上とぼかした表現になっているが、この拡大図を見ると上側に9シャーシ、下側に9シャーシが搭載されており、キャビネットには18シャーシ、216ノードが搭載されると考えられる。

京コンピュータではZ軸ループにIOノードが挿入されており、そこからファイルシステムやユーザターミナルに繋がっている。キャビネットの拡大図を見ると、上下の各9シャーシの間に別種のシャーシがあり、この部分にIOノードが搭載されていると考えられる。

うがった見方をすると、IOノードには左右からの冷却水パイプが書かれておらず、この部分は空冷と思われる。また、Z軸はキャビネット内の18シャーシとIOノードを繋ぐリングになっているのではないかと思われる。

そして、スパコン開発のロードマップとしては、このPost-FX10スパコンは2015年ころに発売の予定となっている。そして、2014年ころからはExa-System開発の国家プロジェクトが始まることになっている。