NECは、SC13の直前の11月15日に次世代ベクトル型スパコン「SX-ACE」を発表し、コロラド州デンバーで開催されたSC13で展示と発表を行った。前世代のSX-9は2007年の発表であるので、実に6年ぶりの新スパコンの発表である。

また、NECはブースでの展示に加えて、ベンダーフォーラムでSX-ACEの技術と将来のロードマップの発表を行った。発表者は4月に横浜で開催されたCool Chipsのときと同じ百瀬氏である。

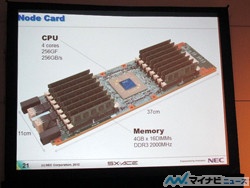

SX-ACEでは、中心となるベクトル演算プロセサが1チップになった。それにメモリDIMMをつけるだけでベクトル計算ノードを構成できるので、次の図のように非常にすっきりとした構成となった。このカードを2枚平置きにして、CPUには水冷のコールドプレートを付けて2ノードモジュールとしている。

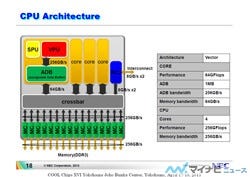

SX-ACEのプロセサについてはCool Chipsの発表のほうが詳しいので、こちらの資料を使って説明する。スカラ処理を行うSPUとベクトル処理を行うVPU、そしてバッファメモリであるADB(Assignable Data Buffer)で1つのコアを構成しており、SX-ACEのプロセサチップは4コアと16チャネルのメモリコントローラを内蔵している。また、4コアとメモリコントローラを結ぶクロスバと8GB/s×2の外部接続インタフェースを内蔵している。

メモリはDDR3-2000MHzを使い、16チャネル合計で、256GB/sのメモリバンド幅を持っている。Intelのサーバプロセサは4チャネル程度のメモリインタフェースしかもっていないのと比べると、この部分は非常に強力であり、メモリバンド幅重視のNECのベクトルプロセサの特徴的な部分である。

|

|

次世代ベクトルスパコンのCPUチップは、4個のコアと16チャネルのDDR3メモリコントローラをクロスバで接続する。コアはスカラ処理を行うSPUとベクトル処理を行うVPU、そしてキャッシュ的な働きをするADBから構成されている。他の計算ノードとは8GB/s×2のRCUを経由して接続される (出典:Cool Chips 16におけるNECの百瀬氏の発表スライド) |

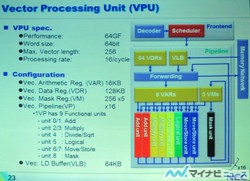

VPUは16本のベクトル演算パイプを持ち、各演算パイプは、毎サイクル、倍精度浮動小数点の加算と乗算をそれぞれ2演算行うことができる。また、これに加えて、除算/開平演算、論理演算、ロードストア、マスクの演算器を持っている。加算と乗算でいうと各パイプラインは1サイクル4演算で、16ユニットで合計64演算、これが1GHzのクロックで動くので、VPUのピーク演算性能は64GFlopsとなる。そしてチップには4個のVPUが搭載されているので、ピーク演算性能は256GFlopsとなる。なお、SPUも浮動小数点演算器を持っており、この部分の演算性能を加えて276GFlopsと書いている資料もある。

|

|

VPUは16本のベクトルパイプラインを持ち、各パイプラインは加算2ユニット、乗算2ユニット、ムーブ/ストア2ユニットと割り算/SQRT、論理演算、マスクの計9ユニットを含んでいる (出典:Cool Chips 16におけるNECの百瀬氏の発表スライド) |

ADBは1MBと容量はさして大きくないが、VPUとのインタフェースは256GB/sのバンド幅を持ち、この部分で見ると、伝統的なベクトルマシンの4Byte/Flopのメモリバンド幅/演算性能比となっている。

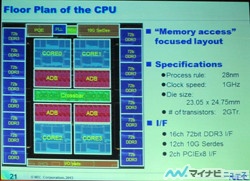

プロセサチップは28nmプロセスで作られ、23.05mm×24.75mmとかなり大きなチップで、総トランジスタ数は2BTrである。

|

|

SX-ACE CPUチップのフロアプラン。28nmプロセスを使い、23.05mm×24.75mmのチップで、クロックは1GHz動作 (出典:Cool Chips 16におけるNECの百瀬氏の発表スライド) |

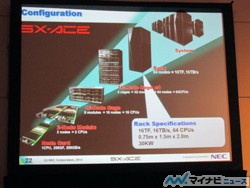

SX-ACEの実装は、ノードカード、それを2枚搭載した2ノードモジュール、8個の2ノードモジュールをまとめた16ノードケージ、そして4台の16ノードケージを搭載するラックという階層になっている。

ラック1本に合計64ノードが収容され、全体で16TFの倍精度浮動小数点演算性能と16TB/sのメモリバンド幅を持つ。消費電力は30kWである。ラックは0.75m×1.5m×2mで、標準の19インチラックよりも大きなサイズのラックを使っている。

各ノードからは8GB/s×2のインタコネクトが出ており、これを2段のFat Treeで接続して、最大512ノードのシステムが構成できるようになっている。各ノードが256GFlopsであるので、この最大規模のシステムは131TFlopsとなる。131TFlopsの規模で比較すると、SX-9は80ラックを必要とし、設置面積は288m2、消費電力は2.4MWであったが、SX-ACEでは8ラックで済み、設置面積は56m2と1/5になり、消費電力は0.24MWと1/10になっているという。

ペタFlops級のスパコンが多く作られている現状で、最大規模が131TFlopsというのは小さいのではないかと、展示ブースの説明員に聞いたところ、Fat Treeのスイッチを拡張すれば、より多くのノードを接続することができる設計になっているが、現在の商品としては512ノードまでとなっているという回答であった。また、なぜSX-10(あるいはローマ数字でSX-X)ではないのかと聞くと、SX-10はすでに商標登録されており、使えなかった。このため、名前を変えたとのことであった。

また、SC13のベンダーフォーラムで、百瀬氏はNECの次世代スパコンの開発にも言及した。NECはAuroraというコードネームで次世代のスパコンの開発プロジェクトを始めており、2016年~2017年ころに次世代機を発売する予定であるという。

Auroraの詳細は明らかにされなかったが、NECのスパコンの伝統を受け継ぐ、高演算性能、高メモリバンド幅のビッグプロセサとなるが、アーキテクチャ的にはこれまでのSXから大きな変更になるという。今回のSX-ACEも1ボード1ノードであるが、Auroraでも1ボード構成をとり、PCやサーバへのアドインカードから、多数のノードカードを高密度で実装する水冷のスパコンまで、広い範囲の製品を作ることを目指しているという。