2nmプロセス以降を実現するために必要な技術とは?

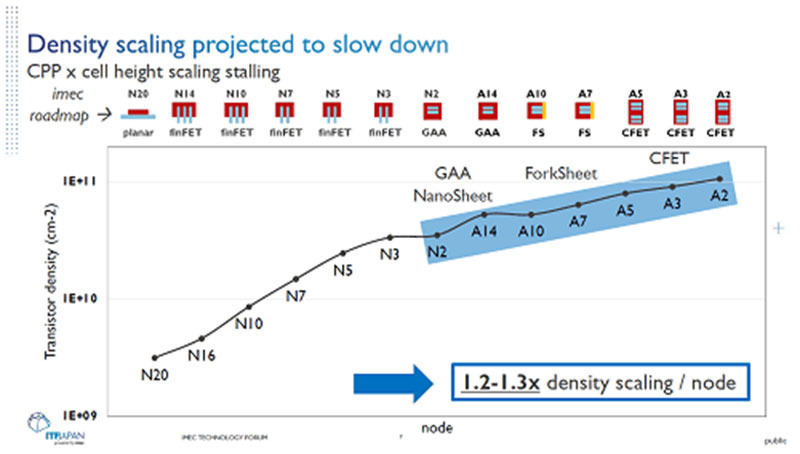

imecのロジックデバイス担当VPであるJ.Ryckaert氏は 、2Å(=0.2nm)に相当するA2プロセス(2036年に実用化か?)までのimecのロードマップを示した。

トランジスタ構造は、N2(=2nm)プロセスから現在のFinFETからGAA(ゲートオールアラウンド)に変わるが、A14(=1.4nm)プロセスからは食器のフォークの形状に似たFS(フォークシート)構造が採用され、さらにA1(=1nm)プロセスからはnMOSとpMOSを縦に重ねるCFET構造にかわるとしている。

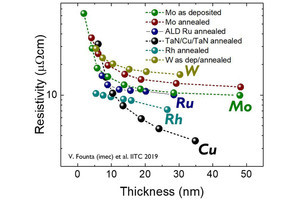

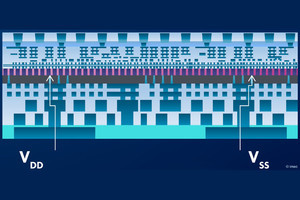

また、FEOLでのトランジスタ構造の進化だけではなく、BEOLでも、多層配線構造や材料が進化しようとしている。従来は半導体チップの表面側からトランジスタへの電源供給を行ってきたが、N2プロセスからは裏面から電源供給することで表面の空いたスペースにトランジスタで埋めることで、集積度を挙げるBSPDN形成プロセスの開発も進んでいる。また、超微細化で抵抗が急増してしまうCu(銅)にかわる新しい配線材料の探索も行われている。

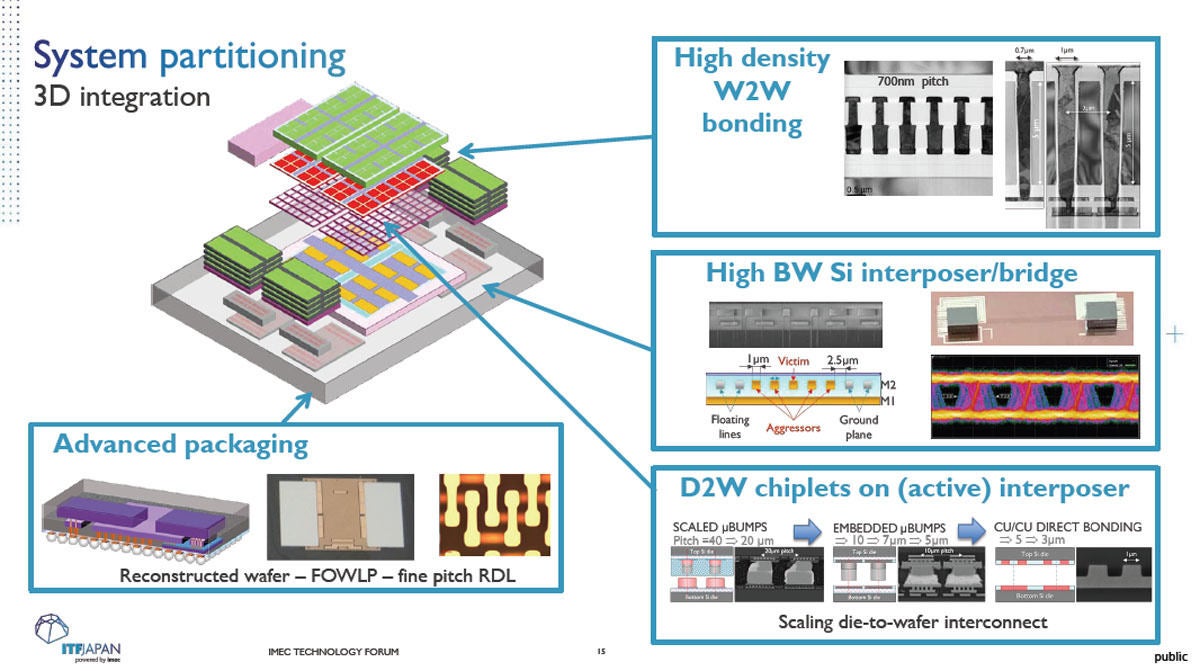

トランジスタ密度の増加カーブ(図2)は、N2プロセス以降緩くなると予測されるが、それをカバーして単位面積当たりの集積度を挙げる手法が3次元化である(図3)。

-

図3 ヘテロジニアス3次元実装。高密度ウェハ・ツー・ウェハボンディング、高帯域シリコンインターポーザー/ブリッジ、インターポーザー上のダイ・ツー・ウェハチップレット、先進パッケージングなどさまざまな技法を採用

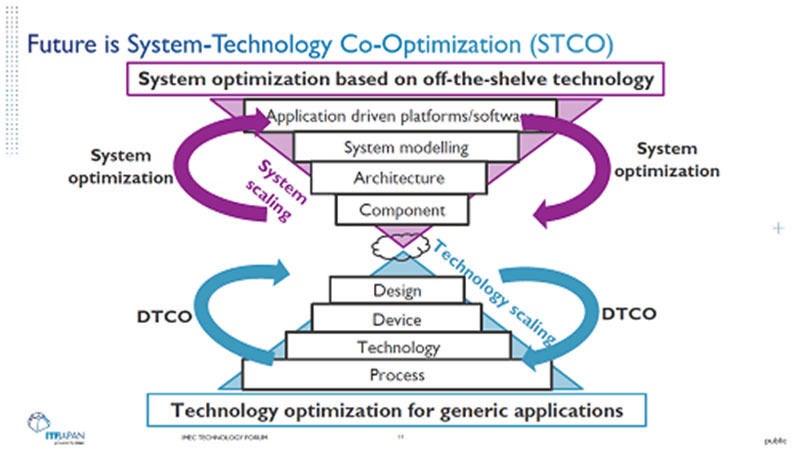

ムーアの法則をさらに進展させるために集積システム構成と回路設計とプロセス技術との同時最適化であるSTCO(図4)が今後は必要になるとRyckaert氏は強調した。特にさまざまなチップレットを搭載した3DICを実現するためには、集積システムからプロセス技術に至る同時最適化が必須であるとしている。