マシンラーニングに最適化されたプロセサ

ArmはHot Chips 30において第1世代のマシンラーニングプロセサを発表した。Armは2018年2月にマシンラーニングプロセサやニューラルネットの開発ツールなどを含むIP(Intellectual Property)スイート「Project Trillium」(コードネーム)を発表している。最初の発表では、マシンラーニングプロセサの構造などは発表されなかったが、今回のHot Chipsでは内部構造が発表され、中身が見えてきた。

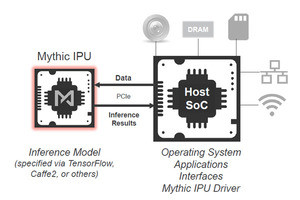

Armのマシンラーニングプロセサはゼロから設計したマシンラーニング向けに最適化したアーキテクチャのプロセサで、CPU、GPU、DSPなどと比べて大幅に効率が高い。そして、オープンソースのソフトウェアスタックが使え、容易に使用できるという。

このプロセサのアーキテクチャはIoTからサーバや自動運転までスケールするが、最初のターゲットはモバイルデバイスとその派生セグメントであるという。

-

ArmのMLプロセサのアーキテクチャは、マシンラーニングのためにゼロから開発したもので、CPU、GPU、DSPと比較して効率が高い。最初のターゲットはモバイルデバイスとその派生領域である (出典;この連載のすべての図は、Hot Chips 30におけるARMのIan Bratt氏の発表資料のコピーである)

16個のCompute Engineを搭載

Armのマシンラーニング(ML)プロセサは次の図に示すように、16個のCompute Engineを持っている。畳み込み演算のスループットは1GHzクロックで動作させた時、~4Top/sとなる。推論が主な用途であるIoT向けのプロセサとしては、計算精度はINT8で良いというのがコンセンサスになってきており、Arm MLプロセサも演算は8bitの整数で行っている。

INT8演算なので電力効率は高く、7nmプロセスを使う場合、電力効率は3Tops/Wを上回るという。また、チップ面積は~2.5mm2である。

なお、このIPは今年中(2018年)にリリースされる予定である。

ArmのMLプロセサの4つの特徴

ArmのMLP(Machine Learning Processor)の4つの主要な特徴は、(1)静的スケジューリングを行う、(2)効率的な畳み込み処理、(3)バンド幅低減メカニズムを持つ、(4)プログラム可能で柔軟性がある、という点である。

CNN(畳みニューラルネットワーク)の計算順序は解析によって静的に決めることができる。したがって、コンパイラはニューラルネットワークの計算をコマンドストリームに変換してMLPに与えるというやり方をとる。

このやり方をとると、キャッシュが不要になり、フローコントロールも簡単になる。そして、ハードウェア構造は簡単になり、キャッシュミスが無いので性能予測も精度が上がるようになるという。コントロールフローが静的で、命令の発行を含めてロード/ストアのバンド幅が十分にあれば、データをSRAMにプリフェッチすることができるので、キャッシュでなくともSRAMでも同等の効果が得られると思われる。

1プロセサあたりの演算性能はどの程度か?

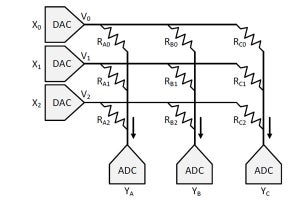

畳み込み処理は、入力(Input Feature Maps)にフィルタを適用して出力(Output Feature Maps)を計算するが、フィルタを適用する位置をスライドさせながらOFMの要素を1つひとつ計算するので計算量が多い。しかし、原理的にOFMの各要素の計算は独立で、並列に計算を行うことができる。また、一般に何枚ものフィルタを使い、フィルタの枚数だけのOFMを作るが、この計算もOFMごとに独立であり、並列に計算することができる。

Arm MLPではOFMをCompute Engine(CE)に割り当て、CEのSRAMにそのOFMの計算に使うフィルタの係数を格納して処理を行う。このようにすることにより、繰り返し使用されるフィルタの係数を外部メモリから読んでくる回数を減らしている。また、IFMはSRAMのすべてのバンクに格納し、並列にアクセスすることにより、読み出しバンド幅が大きくなるようにする。

MACエンジンは2×8×16=256ops/cycleの演算ができ、チップには16個のCEがあるので、MLP全体では4096ops/cycleの演算能力がある。クロックが1GHzの場合は、4.1Topsの演算性能を持つ。なお、内積の計算は8bitであるが、アキュムレータでの加算は32bit整数で行っている。

(次回は9月20日に掲載します)