6月にドイツで開催された「ISC 2019」において北京航天大学(Beihang University)兼 中山大学(Sun Yat-sen University)のDepei Qian教授が中国が進めるエクサスケールスパコンの開発状況について発表を行った。

中国がエクサスケールを目指す理由

中国のエクサスケールスパコンの開発目標は、自分でコントロールできるテクノロジでエクサスケールのスパコンを作り、国立のHPC環境で使えるようにすることである。また、重要なドメインのアプリケーション開発や研究をサポートすることである。

そのために達成すべき目標として、ピークで1ExaFlopsの演算性能、10PBのメモリ容量、ExaByteのストレージ。電力効率は30GFlops/W、400Gbps以上のインタコネクトを上げた。

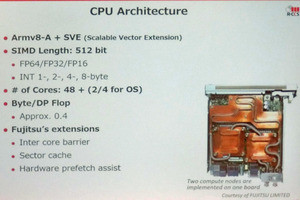

日本の次世代スパコン「富岳」はピーク演算性能が約0.4ExaFlops、電力効率は15GFlops/Wであるので、演算性能、電力効率の点で中国の目標は富岳の2倍である。また、富岳のHBM2メモリは0.48PBしか容量が無く、次の階層としてDRAMや高速のNVRAMなどが付けられると思われるが、メモリ容量が小さいのは気になる点である。

そして、Qian教授は、大規模資源の効率的なマネジメント、使いやすい並列プログラム開発環境、巨大システムを高信頼で動かすため、システムの監視や耐故障性などの重要性を指摘した。

-

中国のエクサスパコンは1ExaFlopsのピーク演算性能と30GFlops/Wの電力効率を目指す。そして、10PBのメモリを持つ (このレポートのすべての図は、ISC 2019でのQian教授の発表資料を撮影したものである。プロジェクタの表示周期と露光タイミングの関係で、影がでている写真もあるが、ご容赦願いたい

アーキテクチャとして重要な点として、計算パワーとメモリ能力をマッチさせることを挙げた。これは中国の巨大スパコンがメモリ能力に比べて巨大な演算能力を積んでTop500のランキングを上げていたことの反省であると思われる。

そして、具体的には計算ユニットとメモリを近づけるDRAM in ProcessorやPIM(Processor in Memory)アーキテクチャを検討項目として挙げている。また、データの移動中にデータを加工するようなアーキテクチャも検討するという。

また、ドメインスペシフィックなアーキテクチャやダイナミックに再構成可能なアーキテクチャを検討する。後者はスイス・アーミーナイフ(マルチツールナイフ)のように、必要となったときに、その用途に向いた機能ユニットを出してきて効率の良い処理を行うというイメージである。

また、新たに広がってきたニューロモルフィックな処理、グラフ処理、マシンラーニングへの対応も必要であるという。

この辺りの指摘は、至極当然であるが、具体的にどのようにやるのかという話はされなかった。

ボトルネックとなるメモリへのアクセス

そして、プロセサとメモリの性能ギャップは増大しており、計算を行う上で、メモリアクセスが主要なボトルネックになっていると指摘している。これも当然の指摘で、日本の富岳はメモリ能力の強化を優先している。

また、メモリ容量を増やし、性能を上げ、電力を減らす解決策として、MTJ(磁気トンネル接合)を使う不揮発性メモリの採用を挙げた。また、DRAMとMTJの不揮発性メモリとの組み合わせで両者の長所を組み合わせるという手もあると述べた。

プロセサとメモリの距離の短縮については、下の図のような3DメモリやDRAM in ProcessorやMemoryの中に処理機能を組み込むなどの案があると指摘した。

また、色々なメモリが出てきており、メモリ階層が増えていくが、データ移動を減らしデータの再利用を増やすような構造やプロトコルが重要になるという。

そして、インタコネクトは、システムの性能と安定性にかかわるキーコンポーネントと指摘し、エクサスケールのシステムではインタコネクトの消費電力は無視できなくなっているという。

具体的な目標として。100Kノードを超える接続を安定的に実現する。400GBps以上の通信速度を持ち、1μs以下のレーテンシ。さらに、低電力、安定性を挙げた。その実現手段として光ファイバの使用を挙げたが、現状では小型化がネックであるという。

エクサ時代に求められるシステムソフトの有り様

システムソフトウェアは変化するアーキテクチャやアプリケーションに対応できることが重要であると指摘し、エネルギー消費をコントロールする機能も必要と述べている。

データフローやデータ駆動の言語のコンパイラが必要である。それらはヘテロでメニ―コアのアーキテクチャで最適化を行えることが必要になる。

また、効率的なデバグが行なえることが重要で、リプレイをする時のオーバヘッドが小さいこと、エラーを検出した時に、それはコーディングが悪いのか、ハードウェアがフォールトを検出したのかが切り分けやすいことも必要である。そして、ヘテロ性を吸収するランタイムを用意することも重要であると指摘した。

並列プログラミングは、どのように並列性を記述するか、タスクをどのように分割するかに始まって、同期やデータ依存性、レーシングなどの問題があり、難しい。また、並列プログラムの動作は一般に非確定的であり、デバグが難しい。そして、共有リソースの取り合いなどから、性能も一定しない。これにヘテロ性が加わると、問題はさらに複雑になる。

したがって、並列プログラムの開発には、プログラムモデルから、コンパイラ、並列デバグ、ランタイムの最適化、アーキテクチャ的なサポートまで、統合的なアプローチが必要である。

ここまでは、エクサスケールスパコンの実現に伴ういろいろな問題点を指摘し、解となり得るアプローチを列記するという記述で、中国が具体的に何をやっているのかは良く分からない。