COOL Chips 20において、ARMのSr. Architecture Program DirectorのDavid Brash氏とLead ISA ArchitectでARMフェローのNigel Stephens氏がARMアーキテクチャの発展、その中でもスケーラブルベクトル拡張(Scalable Vector Extension:SVE)についての基調講演を行った。

ご存じのようにスマートフォン(スマホ)の大半はARMアーキテクチャのプロセサを使っており、ARMアーキテクチャはどこにでもあるという状態になっている。

現在では、GPUの出荷数でもARMはナンバーワンであり、ARMベースのスマホのユーザは50億人を超える。2016年のARMベースのチップの出荷は167億個、創業以来では1000億個のARMチップが出荷されているという。

|

|

昨年のARMベースのチップの出荷は167億個で、世界中に溢れている。また、ARMはGPUでもナンバーワンになった (このレポートのすべての図は、COOL Chips 20におけるARMの基調講演での発表スライドのコピーである) |

そして、2020年を予想すると、消費者の分野ではVRやARが普及し、より多くの計算能力が必要となる。自動車の分野では運転補助機能の安全性と計算能力の向上が必要となる。企業では5Gや仮想化アプリケーションが使われ、ネットワークエッジでの処理能力の向上が必要となり、スマートシティでは大量のセンサベースのデバイスが使われ、データ処理のニーズが高まると予想される。

64bitのARM v8-Aアーキテクチャは2011年の10月に生まれ、2014年12月にはアトミックオペレーションやタイプ2のVM性能の高速化などを行ったARM v8.1Aアーキテクチャ、2016年1月にはFP16(半精度浮動小数点)サポートやRASなどを強化したARM v8.2-Aアーキテクチャ、2016年10月にはポインタの正当性の検査、多重の仮想化サポートの改良、複雑な演算サポートなどを追加したARM v8.3-Aアーキテクチャと進化してきている。

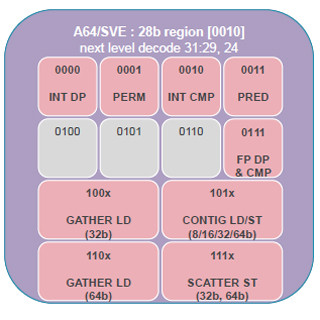

これらに加えて、128bitよりも長いベクトル処理をサポートする「スケーラブルベクトル拡張(Scalable Vector Extension:SVE)アーキテクチャ」を追加した。

|

|

ARMの64bitアーキテクチャARM v8-Aは2011年10月の誕生から、ARM v8.1-A、v8.2-A、v8.3Aと進化してきている。さらに128ビットより長いデータを扱うスケーラブルベクタ拡張を追加した |

このSVEはARMと富士通が協力して開発したものであり、富士通は次世代のExa Flopsを目指すポスト京スパコンに採用すると発表している。

ARMには32bitアーキテクチャのARM v7-Aの時代から進化してきたNEONというSIMD命令があったが、64bitアーキテクチャになるとともにNEONはIEEE 754準拠の演算や64bitの倍精度浮動小数点演算をサポートするようになった。また、128bit長のSIMDレジスタも16個から32個に拡張した。

しかし、64bitのARM v8-Aの市場の広がりから、より強力な拡張が要求され、それに応えるものとしてSVEを開発したという。

SVEではベクトルレジスタの長さは、ハードウェアの選択にまかせて、より強力な演算能力を持たせる場合は長いベクトルレジスタを作り、ハードウェアを小さく抑えたい場合はミニマムの128bit長のベクトルレジスタとするなどの選択が出来るようにした。

そして、ハードウェアとしてのベクトルレジスタの長さがいくらであっても、それを気にせずにプログラムが書けるVector Length Agnosticプログラミングができるというアーキテクチャとなっている。

|

|

基本アーキテクチャの64bit化に伴い、SIMDのNEONも大幅な強化が望まれることになってきた。これに応えるのがSVEである。SVEではベクトルレジスタの長さをハードウェアが選べるようになり、一方、プログラムはベクトルレジスタの長さを意識しないで書けるようになった |

NEONでは128bit長のV0-V31レジスタを持っていたが、SVEではこれを拡張して、128bitの1~16倍の範囲の長さのZ0-Z31レジスタを持つアーキテクチャとなった。このレジスタには倍精度、単精度、半精度の浮動小数点数、あるいは64、32、16、8bit長の整数をパックして格納することができる。

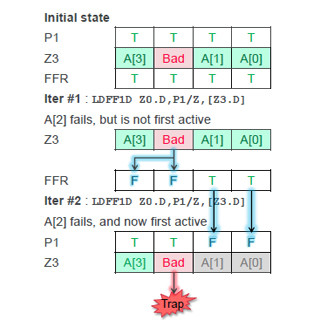

そして、P0-P7のプレディケートレジスタはロード、ストアや演算命令の実行の可否をコントロールし、P8-P15は追加のプレディケートレジスタで、命令の実行をコントロールすることはできないが、プレディケートの一次格納や演算などに使用できる。そして、FFRは最初のフォールトを記憶するレジスタである。

ZCR_ELxはベクトルレジスタの長さを示すレジスタで、128bitの何倍の長さであるかを示す。

ベクトルレジスタ長に依存しないアーキテクチャは、長いレジスタが必要になっても命令を追加する必要がなく、レジスタの長さが変わってもプログラムを書き直す必要がないというメリットがある。