2023年6月に京都で開催される「2023 Symposium on Technology and Circuits」の主催者が回路設計分野の注目論文を紹介している。その中から今回は、先端メモリとイメージセンサ回路設計関連を紹介する。

先端メモリ設計:TSMC Design Technology Japanが高集積密度の3nm SRAMを発表

- A 3-nm 27.6-Mbit/mm2 Self-Timed SRAM Enabling 0.48 - 1.2 V Wide Operating Range with Far-End Pre-Charge and Weak-Bit Tracking (論文番号:C9-5)

ハイパフォーマンスコンピューティング(HPC)では高い電力効率が求められ、その改善のために最近の設計では動的電圧・周波数制御が広く使用されている。内蔵するキャッシュメモリは、オーバードライブした高電圧での高速な読み出し・書き込み動作と、低電圧での低消費電力動作の両方が強く求められている。

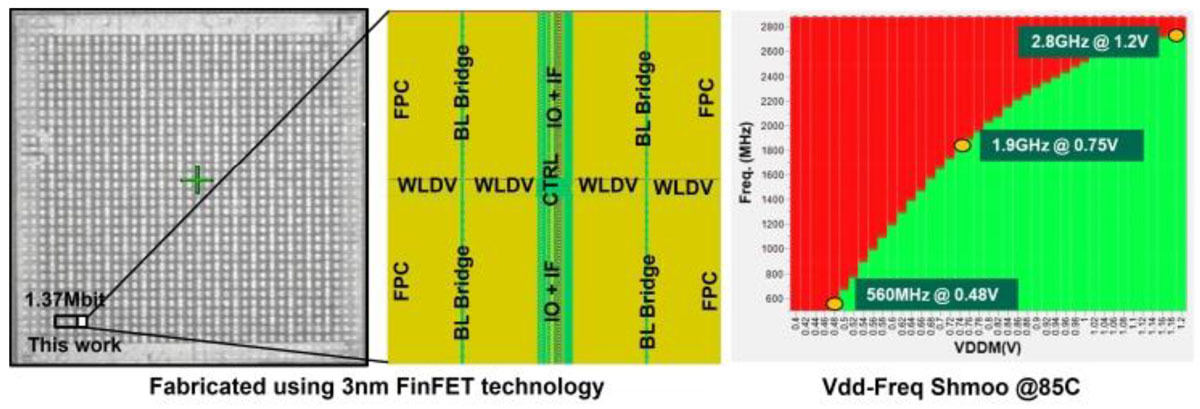

このような背景を踏まえて、TSMC日本法人のデザインセンター(TSMC Design Technology Japan)は、3nm FinFETテクノロジで作製した高エネルギー効率のキャッシュSRAMを発表する予定だという。HPCでは高い電力効率が求められ、その改善のために最近の設計ではDVFS(Dynamic Voltage and Frequency Scaling)が広く使用されている。DVFSはシステムの処理負荷の重さに応じて、電源電圧とクロック周波数を動的に制御して消費電力低減を図る技術である。この発表では、DVFSに対応するために新しい2つのDTCO(設計・プロセス技術同時最適化)技術を報告する予定で、1つはビット線の遠端側にプリチャージ回路を追加配置したこと、もう1つは、広い電圧範囲で最適動作するためのトラッキング回路だという。

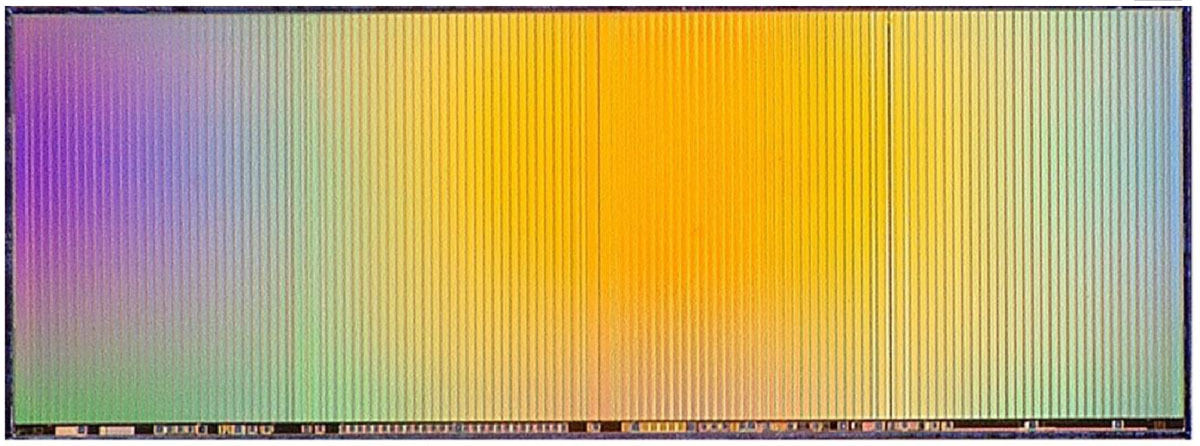

微細化で課題となる(1)配線抵抗の上昇と、(2)トランジスタ特性の電圧依存性感度の増大、に対して改善効果を示している。テストチップはTSMCの台湾ファブにて3nm FinFETプロセスを用いて製造され、27.6Mbit/mm2の集積密度と0.48V~1.2Vで550MHz~2.8GHz動作を実証しており、これまで報告された中でも最高クラスの性能指標(密度×周波数/電圧で定義)を達成したとしている。

-

図1:3nm FinFETプロセスを用いて試作したテストチップの写真、および434kビットSRAMマクロのプロット図、測定した電圧-周波数依存性を示すシュムープロット (出所:VLSIシンポジウム委員会、以下すべて)

先端メモリ設計:キオクシアが高ビット密度1Tb3ビット/セル3D-NANDフラッシュメモリを発表

- A 1Tb 3b/Cell 3D-Flash Memory of more than 17Gb/mm2 bit Density with 3.2Gbps Interface and 205MB/s Program Throughput (論文番号:C2-1)

NAND型フラッシュメモリ設計で、ビット線、ワード線を分割し、負荷を軽減することは高密度化の有効な手段である。しかし、高ビット密度化のためのワード線スタックやハイブリッド行アドレスデコーダ(X-DEC)などの周辺回路面積の増加は、ビット高密度化の進展の妨げになっていた。

この課題に挑戦したキオクシアは、17Gb/mm2を超えるビット密度の210以上のワード線層を用いた1Tb 3ビット/セル 3Dフラッシュメモリを報告する予定だという。

8物理プレーン構造により、40μsの低リードレイテンシと205MB/sの高いプログラムスループットを実現している。X方向のデータ入出力DQ面積を41%に削減することで、3.2Gbpsの高速インタフェースを実現している。ハイブリッド行アドレスデコーダ(X-DEC)は、配線混雑の課題に対応し、読み取りレイテンシの低下を最小限に抑えることができる。1パルス2ストローブ技術により、センシング時間を18%短縮し、205MB/sのプログラムスループットを達成したとしている。

イメージセンサ設計:ソニーがSPAD画素を用いたフォトンカウントイメージセンサを開発

- A 3.36μm-Pitch SPAD Photon-Counting Image Sensor Using Clustered Multi-Cycle Clocked Recharging Technique with Intermediate Most-Significant-Bit Readout (論文番号:C15-2)

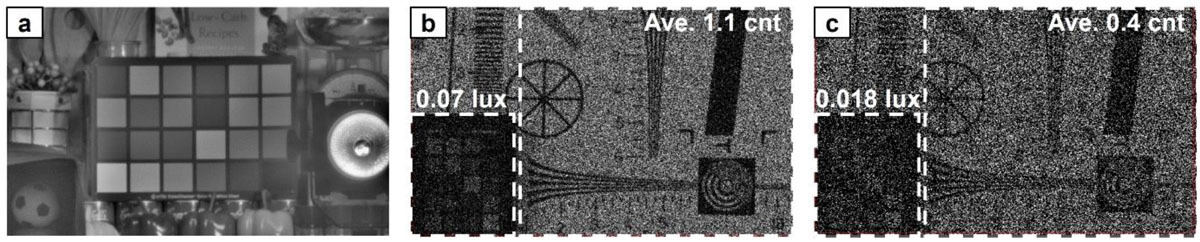

SPAD(Single Photon Avalanche Diode)画素を用いたイメージセンサは光子1個を捉えてその反応回数を直接数えることで画像を作り出すため暗い場所でも撮影ができるイメージセンサとして期待されている。一方で、SPAD画素に光子が入った回数を数えるため明るいシーンではカウント数が増大し回路規模や電力が増大してしまう課題があった。

ソニーグループからの今回の発表では、SPAD画素のリセットを周期的に制御することで明るいシーンにおけるSPAD画素反応を抑えて電力を抑えることを可能にしたこと、ならびにカウント回路の最上位桁(MSB)の変化の回数を数えることで上位桁を計数し、画素に集積するカウント回路を8bitに抑えることで画素サイズの小型化も実現したことが報告される予定だという。22nmプロセスを採用することで画素サイズ3.36μm□を実現したとしている。