回路設計分野の採択率は34%、日本勢は16件が採択

2023年6月に京都で開催される「2023 Symposium on Technology and Circuits」の回路設計分野には、359件の応募があり、123件採択された。採択率は34%だった。このほか、Late News(一般応募締め切り後に緊急性の高い論文受付)に11件の応募があり、1件だけ採択された。

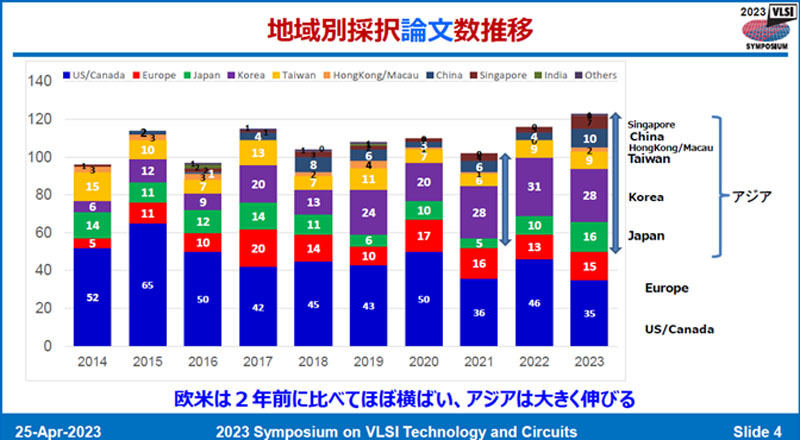

地域・国別の応募件数では、70件以上だったのは米州(86件)、韓国(79件)、中国(73件)の3地域・国だったが、採択件数は、米州35件(採択率41%)、韓国28件(同35%)、中国10件(同14%)だった。日本は23件の応募で16件が採択と採択率70%となっている。アジアからの応募件数と採択論文数が目立って増えており、特に、中国の10件ならびに日本の16件の採択は過去10年間で最多である。投稿論文のうち大学からの応募が8割を占めていた。

採択論文の機関別発表論文件数ランキングは、韓KAISTが9件、Samsung Electronicsが7件、国立シンガポール大学が6件、東京工業大学(東工大)、中国精華大学、韓POSTECH、Intel各4件の順番となっている(3件以下は省略)。

日本勢の採択論文16件に限ってみると、トップの東工大の4件に続くのは、ソニーの3件、東京大学、半導体エネルギー研究所、TSMC Design Technology Japanが各2件、キオクシア、ルネサス、日立製作所が各1件となっている。このうち、TSMC Design Technology Japanというのは、横浜にあるTSMCのデザインセンターで、VLSIシンポジウムに初登場しかも2件採択という点で注目を集めている。TSMCが日本で半導体設計技術開発に注力しており着実に成果が上がっている様子が読み取れる。

回路設計分野の注目論文は14件

VLSIシンポジウム委員会は、デバイス・プロセス技術分野同様、回路設計分野(一部、技術分野との融合分野を含む)の注目論文を14件公開した。まずは、IntelとMediaTekそれぞれによる注目論文2件を紹介する。

高集積プロセッサ設計:Intelが裏面電力供給をIntel 4 E-Coreに実装

- E-Core Implementation in Intel 4 with PowerVia(Backside Power)Technology(論文番号:T1-1)

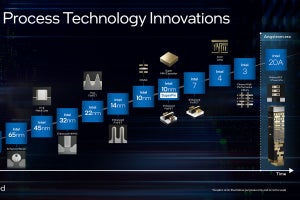

表面のメタル資源を100%信号配線に使うことができ、裏面での低抵抗相互接続を可能にするパワービア(Intel独自の裏面電力供給網の呼称)の採用が、電力、性能、面積向上につながることが知られていたが、その実デバイスへの実装が待たれていた。

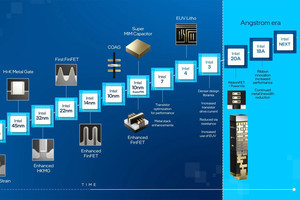

Intelはこの度、高収力裏面電力供給を可能にするパワービアテクノロジーを開発し、そのテクノロジーを用いたE-Core(高効率コア)への実装について報告する予定。パワービアはムーアの法則を持続させる革新的技術であり、この技術によりIntel 4(他社の4nmプロセス相当)のE-Coreにおける標準セル使用率を広い領域で90%以上とすることに成功し、IRドロップを削減することで5%以上の周波数改善も可能にした。

スループット時間はやや長いが許容範囲内であることをシリコン上でのデバッグで実証し、パワービアテストチップの熱特性はロジックの微細化から予想される高い電力密度に見合うものであることも確認したとする。

なお、Intel独自のパワービアテクノロジー自体に関しては別途、発表される予定となっている。

- Intel PowerVia Technology: Backside Power Delivery for High Density and High-Performance Computing(論文番号:T6-1)

AIプロセッサ設計:MediaTekが画像処理向け超低消費電力深層学習システムを開発

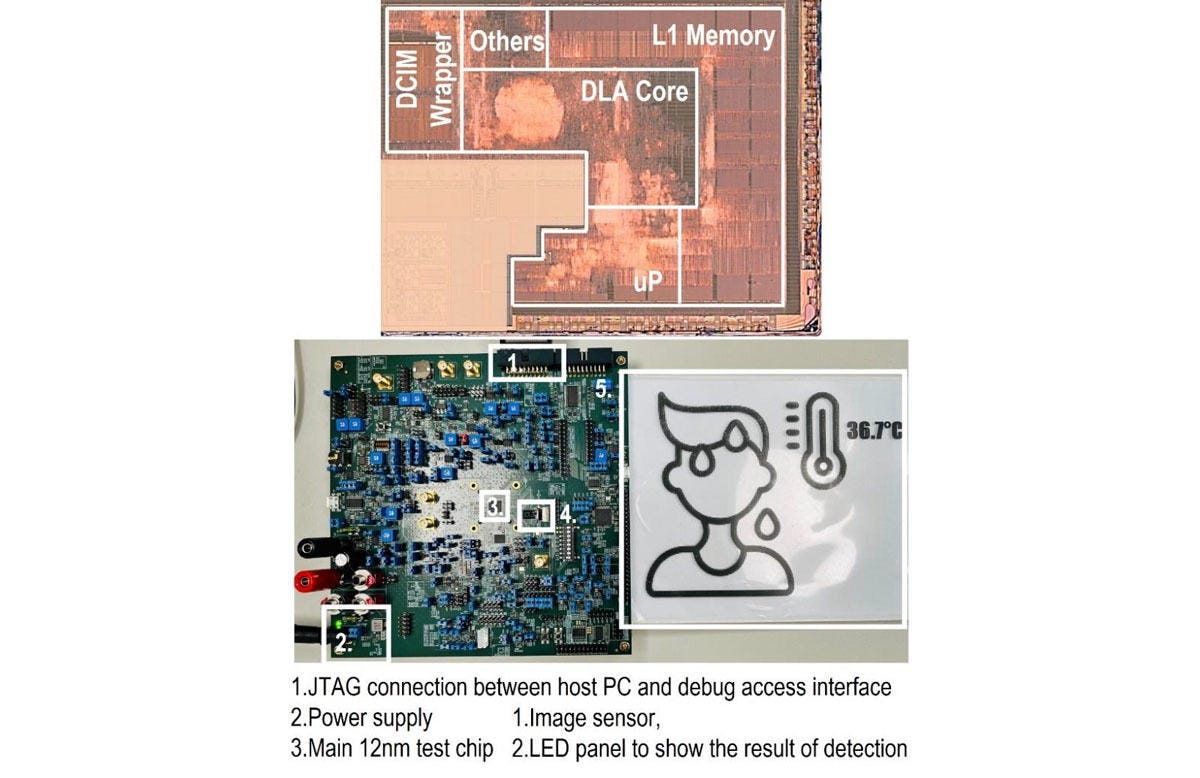

- A 12-nm 0.62-1.61 mW Ultra-Low Power Digital CIM-based Deep-Learning System for End-to-End Always-on Vision (論文番号:C3-4)

バッテリー駆動デバイスが常時機能を活用する際の課題は、計算とメモリを多用するAIアルゴリズムが電力を消費し、デバイスのサービス時間を短くしてしまうことである。そのため、深層学習システムにとって1mW以下の超低消費電力であることは重要な設計制約となっている。

MediaTekは、デジタル計算メモリ(Digital Compute-in-Memory:DCIM)を用いることにより、常時通電可能なエンドツーエンド画像処理向けの深層学習システムを実現したことを報告する予定である。

SoCプロトタイプはDCIMベースの深層学習アクセラレータ(DCIM-DLA)、RISC-Vマイクロプロセッサ、イメージセンサインタフェースで構成されている。DCIMは要求正解率と消費電力のバランスを実現する混合演算精度をサポートしている。測定されたピーク性能は51.2GOPS、エネルギー効率は57TOPS/Wであり、MobileNet-V1モデル上に構成された混合演算精度による人物検知タスクにて85.7%の正解率を達成、またイメージセンサを除くエンドツーエンドシステムとして2および15fps動作時にそれぞれ0.62ならびに1.61mWの消費電力であると報告している。