最近増えてきているAIアクセラレーターを中心とした半導体デザイン会社の情報を見ていたらTenstorrent社が気になった。

一昨年かなり高集積のAIアクセラレータ「Gray Skull」を発表したと思ったら、昨年末にはRISC-VベースのCPUデザインを完成し、IPライセンスを始めるという。私がTenstorrent社に興味を持ったのは、永年AMDでCPUデザインを手掛けたCPUアーキテクトのJim Kellerが移籍し、社長(兼CTO)を務めるというニュースに接したからだ。知人の話によると、業界での有名人Kellerはいろいろなイベントに出て将来のコンピューター・アーキテクチャーについて積極的に発言しているという。そこで昨年KellerがTSMCのイベントでプレゼンした模様をYouTubeで見た。Kellerが現在のデータセンター用CPUデザインの諸要件と、それを実現するChipletの将来性について語っているなかなか興味深い内容だ。

Tenstorrent社のJim Kellerのプレゼン

Jim KellerのCPUアーキテクトとしての経歴は華麗だ。DEC、AMD、Apple、Tesla、Intelを渡り歩き、一貫してCPUの設計に携わっている。

特にAMDではK7、K8、そしてZenと現在のAMDの成功を支える数々のアーキテクチャーに直接関わってきた。私がAMDに勤務した時期ともかなり重なるので、一回も面識がなかったのが不思議なくらいである。その後のインタビュー記事などを読むと、本人は大きな組織を束ねる仕事よりも新しいコンピューターを考えることに喜びを感じているらしく、私がK7を必死になって売っていた時期には、小さな設計チームでK8の構想を練っていたのだと思う。大企業でのCPUアーキテクトとしての多大な経験を生かして、現在、100人にも満たないスタートアップTenstorrent社(2016年創立)に一昨年に移籍した。

Tenstorrent社は一昨年、「人間の脳のように動く」という意味合いを込めた、AIプロセッサー“Gray Skull”を中心とした関連製品を発表している。Kellerによれば人間の脳は性能、フレキシビリティー、スケーラビリティー、そして消費エネルギーにおいて未だに最高のコンピューターであると言う。その興味はコンピューターアーキテクチャーにとどまらず、半導体プロセスの原子レベルの物理限界から脳科学といった広範囲に及ぶ。

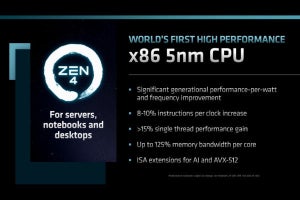

このプレゼンでKellerは多種多様なタスクと級数的に増加するワークロードに対応するCPUデザインの最適な方法はChiplet技術であると主張する。従来のCPUの設計手法は、微細加工の発展とともに、より高性能なCPUコアを中心に据えて、システム全体の性能向上をするために周辺回路をモノリシックに集積するという方法であったが、Chiplet技術はその発想を変えてCPUコアのダイ(プロセッサーチップ)と入出力などのサポート回路を別個のダイにして、高密度に接続実装することで1個のマイクロプロセッサーを実現する方法である。AMDがZenアーキテクチャー採用のデスクトップCPU「Threadripper」やサーバー向けの「Epyc」で積極的に採用した方法で、Chipletに組み込まれる各々のチップの製造プロセスは異なっている。

Kellerが強調する点は、より多様化するタスクと増加するワークロードに対応するためには、最新のCPUコアをサポートするDDR3/4/5/6のような異なるメモリーに対応するコントローラーは、その要件に応じて別チップで対応する方がコストとタイムリーな市場投入を考えた場合断然優位である、という点だ。そのためには他企業との「協業」が重要で、問題解決にはオープンで緊密な協業スキームが求められると指摘する。

この点で、かつてマザーボード、チップセット、メモリーインタフェースを含めるCPUのエコシステム全体を掌握しようとした巨人Intelに、他社との協業で対抗勢力を立ち上げようとしたAMDのDNAをKellerが継承しているような印象を持った。確かに、一昨年末までの空前の半導体供給不足で誰の目にも明らかになったのは、システムの総体は最先端のプロセスを駆使した最新CPUだけでは構成できず、旧世代プロセスで製造した他の周辺チップの入手なしには可能とならないことである。そういえば、かつて自社Fabを運営していたAMDでも、最先端技術を使用したCPU以外のチップセットなどの周辺チップは旧世代のプロセスで製造していた事を思い出した。

協業スキームの重要性を強調するKellerの結論は、「CPUソリューションの今後はRISC-Vのようなオープンアーキテクチャー環境で自由な発想を取り入れたCPUコアと独自設計のAIプロセッサーを中心に据えて、I/Oなどの周辺チップは他社から調達し、全体をChipletで構成する。さらにカスタマイズが必要ならばFPGAを使って実現すればよい」、という明確なもので、これこそがTenstorrent社が目指すことであると語る。ムーアの法則限界説が聞かれる昨今、「まだまだこれから」と胸を張る業界のレジェンド・アーキテクトによる自信たっぷりのプレゼンにはさすがに説得力がある。

Designing in 2023: 10 Problems to Solve w/ Jim Keller

Chipletを駆使した製品を発表するAMDとIntel

そんなプレゼンを見ながら感心していたら、タイミングよくAMDから新製品、第4世代Epycが発表された。HPC向けのこの製品はなんと1つのCPUパッケージに96個のCPUコアを内蔵するという大掛かりなチップだ。

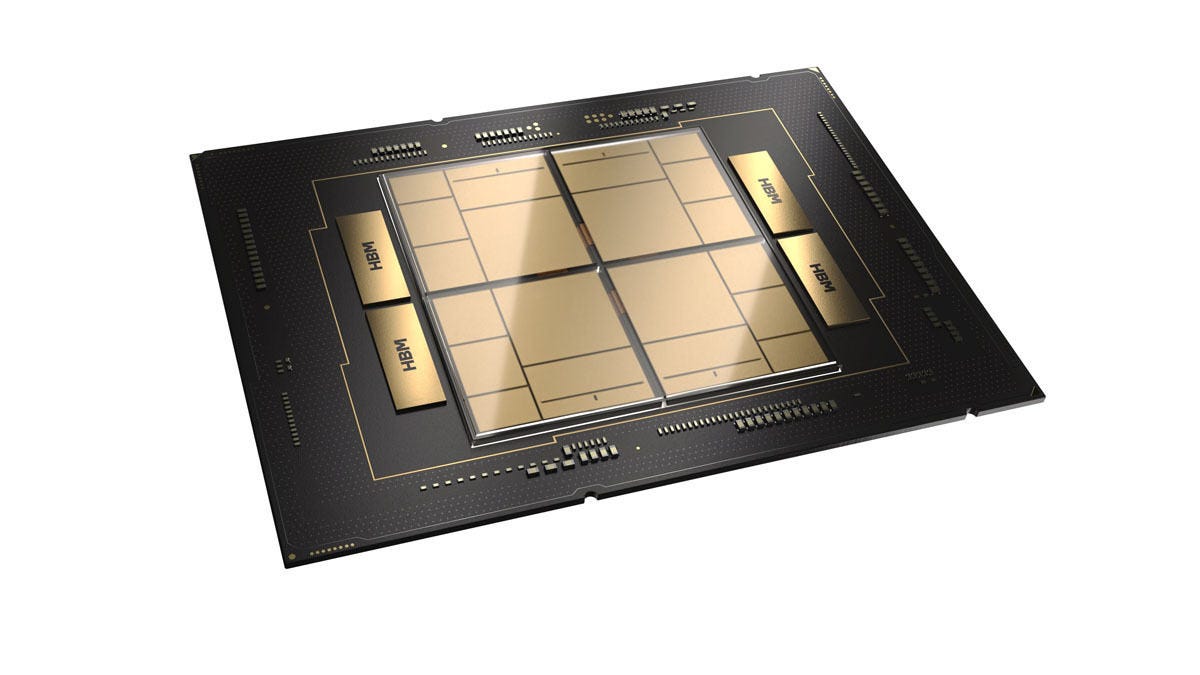

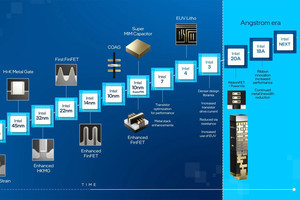

もちろんChipletの形で提供され、I/OチップをCPUに集積せずに、外部のチップで実現することでパッケージ全体のCPUコア数を最大化することに成功している。ごく最近では、Intelがかねてよりコードネーム「Saphire Rapids」として開発してきたCPU製品がやっと発表された。度重なる遅延を経てやっとリリースされたこの製品は、AMDに対抗する第4世代Xeonスケーラブル・プロセッサとXeon Maxとして発表された。かなり難産だったこの製品の評価はこれからの市場の反応を待つとして、AMDとIntelの両社の最先端製品はともにCPU、AIアクセラレーター、メモリーコントローラーを別個のチップによってChipletに実装した超ハイエンドの製品で、引き続きデータセンターのCPUトレンドを牽引する予想であるが、Tenstorrentをはじめとする新興デザインハウスが虎視眈々と市場参入を狙っている。

モノリシックチップの集積度を上げることによってひたすら周辺回路の取り込みを目指したかつてのCPUデザインの歴史を牽引し、今ではスタートアップのCTOとしてChipletによるCPUデザインの新時代を熱っぽく語った業界レジェンドの言葉の重みをあらためて実感した。