Intelは、12月3~7日にかけて米国で開催中のIEEE International Electron Devices(IEDM 2022)において、同社のエグゼクティブVP兼技術開発ゼネラルマネージャであるAnn Kelleher氏が「Celebrating 75 Years of the Transistor! A Look Ahead Towards the Next Generation of Innovation Opportunities」と題しや基調講演を行い、これまでよりも10倍の実装密度を達成した3Dパッケージング技術や、RibbonFET(一般にGate-All-Aroundと呼ばれるトランジスタ構造のIntelでの呼称)の先を見据えたトランジスタのスケーリング(微細化)、わずか原子3個分の厚さの超薄素材を含めた新素材の導入、高性能コンピューティングをさらに高度化するエネルギー効率とメモリの新たな可能性、量子コンピューティングのさらなる進歩といった、Intelにおける最先端半導体研究についての紹介を行った。いずれの技術も「Intelが、この先何年にもわたりムーアの法則を順調に存続させていくために必要なブレークスルー」(Kelleher氏)だという。Intelは、これらの技術を統合して、2030年には1パッケージに1兆トランジスタの搭載を目指すという。

IEDM 2022で、Intelはムーアの法則を継続するための3つの主要領域すべてにわたって、革新的技術を発表した。

その領域とは、以下の通り。

- 1チップ上に実装できるトランジスタ数を増大する超薄2D素材

- 複数のチップレットをシームレスに統合する新しい3Dハイブリッド・ボンディング接合パッケージング技術

- 高性能コンピューティングをさらに高度化するエネルギー効率とメモリにおける新たな可能性

このほか、量子コンピューテイングに関しても研究の進展状況を発表した。

チップ当たりのトランジスタ数をさらに増大するための超薄「2D」素材

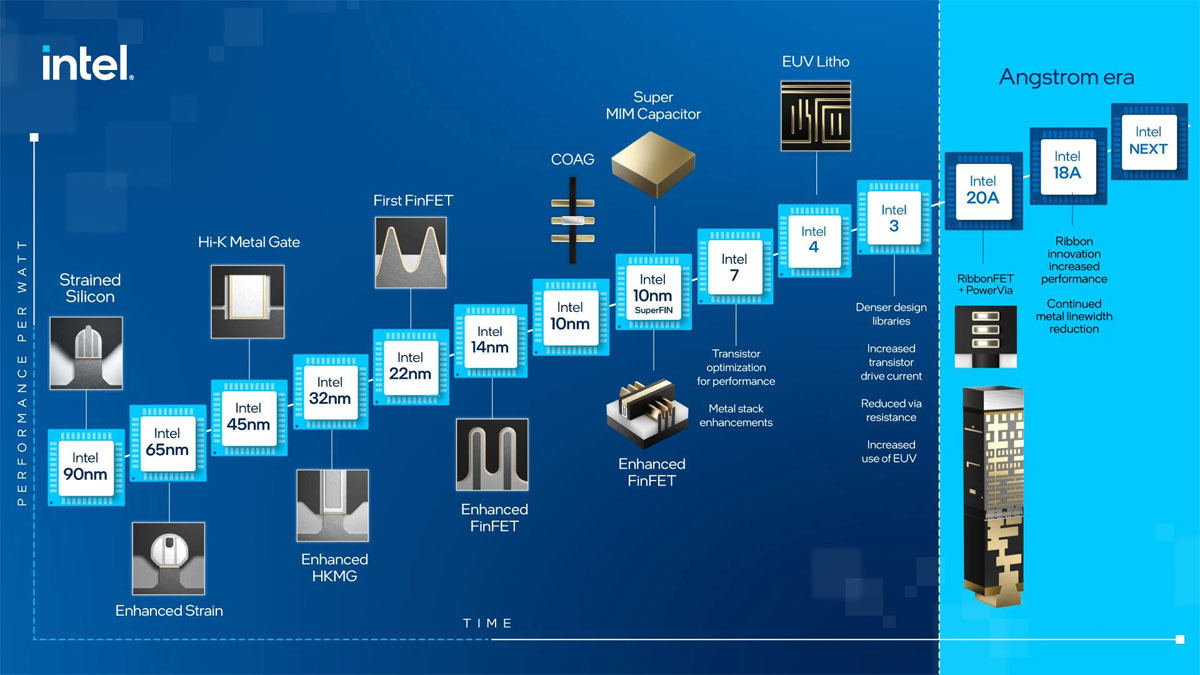

図2は、Intelのロジックプロセスに関する最新のロードマップであるが、「Intel20A (一般に20Åあるいは2nm)」からGate-All-Around(GAA)を採用することを決めている。2030年に向けてチャネルに2D材料を採用することが検討されているが、IntelはIEDM 2022で以下のような発表を行った。

- 原子3個分の厚さの2Dチャネル素材を使用し、GAA積層ナノシートの製作を実証した。同時にほぼ理想的と言える、室温での漏れ電流の低いトランジスタ・スイッチングを達成した。いずれもGAAトランジスタの積層化に欠かせない、重要な2つの進歩である

- 2D素材との電気接点トポロジーに関する初となる包括的分析の成果を発表した。これにより、高性能かつスケーラブルなトランジスタ・チャネルのさらなる進化に向け道が切り拓かれる見込みである

次世代の3Dパッケージング技術に疑似モノリシック・チップを投入

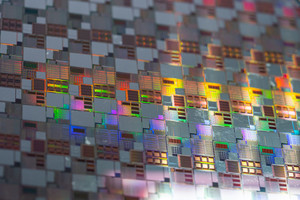

パッケージングは、2.5Dから3Dへ進化を続けているが(図3参照)、IntelはIEDM 2022で以下のようなパッケージ分野の成果を披露した。

- IEDM 2022で公開したハイブリッド・ボンディング接合に関する最新の研究では、電力効率とパフォーマンスの向上を目的に、IEDM 2021で公開した研究成果と比べてインターコネクト密度が10倍向上している

- ハイブリッド・ボンディング接合により3μmピッチまでスケーリングすることで、モノリシックの「SoC」接続で見られるレベルと同等のインターコネクト密度と帯域幅を達成した

高性能コンピューティングの電力効率とメモリに新たな可能性

これらのほか、以下のような成果も発表している。

- チップ領域の利用効率を高めるために、トランジスタ上側の垂直方向に配置できるメモリを開発し、スケーリングを再定義した。Intel初となる、従来の強誘電体トレンチ・コンデンサのパフォーマンスに匹敵し、単一のロジックダイ上にFeRAMを構築できる、積層型強誘電体コンデンサを実現

- デバイスレベルのモデルにより、混合相と欠陥を識別し、強誘電体ハフニウム(Hf)デバイスを改良した。最新のメモリや強誘電体トランジスタの開発に活用される業界ツールにおいて、Intelのサポートを強化

- 5Gの先へさらに一歩近づけ、電力効率の課題を解決するために、300mmのGaN-on-Siウェハ実現に向け、実行可能な開発指針を構築中である。この領域において、業界標準のGaNと比べて20倍のパフォーマンスを実証し、高性能の電力供給に業界記録となるフィギュア・オブ・メリット(性能指数)を達成

- 超高電力効率テクノロジーを飛躍。特に電源をオフにしてもデータを保持して「忘れない」トランジスタという画期的なブレークスルーを実現。研究チームは、室温での完全なテクノロジーの実行/運用を妨げている3つの障壁のうち、2つを打破

- 量子コンピューティングに高品質の量子ビットを提供する革新的な技術を通じ、物理学に新たな概念を導入

なお、同氏は、量子データに影響を及ぼす環境的な妨害要因となりかねない、さまざまな界面欠陥について理解を深めることで、量子情報を格納するもっと有効な方法を見つけようと量子技術分野についても言及している。