ロジックデバイスの超微細化というと、EUV露光やその先の高NA EUV露光を活用した2次元平面回路パターンの比例縮小(スケーリング)やFEOL(Front End of Line)でのトランジスタ構造の変化(プレーナー構造からFinFETを経てGate-All-Around、さらにはCFETへ)ばかりに目が行きがちであるが、トランジスタの超高集積化、つまりトランジスタ密度の増加に対応して、近い将来、BEOL(Back End of Line)の多層配線構造も大きく変わろうとしている。

これまでは、トランジスタの上部に多層配線層を形成して電力を供給していたが、集積度が高まるにつれてこれらの電源供給配線網(PDN:Power Delivery Network)が大きな面積を占有し、単位面積当たりのトランジスタ集積度向上の妨げになっていた。このため、電源供給を裏面側から行うことで、前面側の配線設計の柔軟性を高められるようする提案が行われている。この手法はベルギーのimecで盛んに研究されており、米Intelは2nm世代(Intel 20A)から採用すると発表している。ソニーのイメージセンサ(CIS)も以前は、配線層と画素が同居していたが、配線層を下部に分離することで画素の面積を拡大し感度を向上させているのと同じような発想である。ロジックの場合は、配線層を裏面へと分離することにより、トランジスタ密度を上げようとしている。

日本では未だほとんどなじみのない次世代ロジックデバイスの裏面電源供給ネットワーク(BSPDN:Backside PDN)とその製作プロセス、および将来の応用について、世界最先端の半導体技術研究機関であるベルギーimecでこの分野の研究を主導している著名な2人の研究者が説明する。

これまでのトランジスタへの電源供給方法

半導体チップにおいて、電源供給ネットワークは、電力と基準電圧(つまり、VDDとVSS)をダイ上のアクティブデバイスにもっとも効率的に供給できるように設計されている。

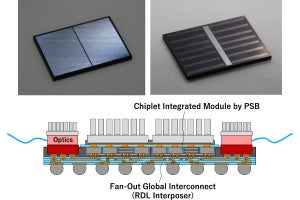

伝統的に、それはウェハの前面でのBEOL(多層配線)プロセスによって製造された低抵抗金属ワイヤの配線網(ネットワーク)として実現されている。電源供給ネットワークは、このスペースを信号ネットワーク、つまり信号を伝送するように設計された相互接続配線網と共有している(図1参照)。

パッケージからトランジスタに電力を供給するためには、電子はトランジスタに近づくにつれて狭くなっていく(したがって抵抗が大きくなる)金属ワイヤとビアを介してBEOL(多層配線工程)スタックの15~20層すべてを通過しなければならないが、途中でエネルギーを失い、IRドロップで電力低下が発生する。電子が、トランジスタの近く、つまり標準セルレベルに到達すると、BEOLのMint層(多層金属配線の最下層)のVDDとVSS)電源、グランドレールにたどりつく。これらのレールは、各標準セル間のスペースを占有している。ここから、各レールは、Middle of Line(FEOLとBEOLの中間の工程)の相互接続ネットワークを介して各トランジスタのソースとドレインに接続される。

表面からの電源供給における問題点

しかし、新しいテクノロジが世代を重ねるごとに、従来のBEOLアーキテクチャは、トランジスタのスケーリングに対応するのが困難になってきている。今日、「パワーインターコネクト(電力相互配線)」は、複雑なBEOLネットワーク内でスペースをめぐってますます競合しており、総体積の20%を占めている。また、電源レールと接地レールはスタンダードセルレベルでかなり大きな面積を占めるため、スタンダードセルの高さのスケーリング(比例縮小)がさらに制限される。システムレベルでは、電力密度とIRドロップが劇的に増加するため、設計者は電圧レギュレータとトランジスタ間の電力損失に許容される10%のマージンを維持することが困難になる。

裏面電源供給ネットワーク(BSPDN)の採用

表面に代えて裏面から電力を供給することにより、これらの問題に対処することができる。

裏面電源供給ネットワーク(BSPDN)というアイデアは、現在強度確保のための支持基板としてしか機能していないシリコンウェハの裏面側に配電ネットワーク全体を移動させることにより、信号ネットワークから電源供給ネットワークを分離するというものである。

これにより、電子が複雑な高層BEOLスタックを通過する必要なく、幅が広く抵抗の低い金属線を介して標準セルに直接電力を供給することができるようになる(図2参照)。このアプローチは、IRドロップを防止し、電源供給性能を改善し、BEOLでの配線の混雑さを減らし、適切に設計された場合、さらに標準的なセルの高さのスケーリングを可能にしてくれる。

|

Naoto Horiguchi

ベルギーimecのロジックCMOSスケーリングプログラムディレクター。 富士通研究所を経て2006年からimecで先端CMOS デバイスの研究に従事し、現在の興味は1nmテクノロジノードを超えた微細化 |

|

Eric Beyne

imecのR&D担当副社長、および3Dシステム統合のプログラムディレクター。1986年からimecで高度なパッケージングと相互接続技術は開発に取り組んでいる。 |

2022年10月21日訂正:記事初出時、執筆者の1人であるNaoto Horiguchi氏のお名前を掲載当初、Naoto Horiuchi氏と表記しておりましたので、当該箇所を修正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。