東京工業大学(東工大)、大阪大学(阪大)、アオイ電子の3者は10月5日、今後の大規模なチップレット集積に求められる、広帯域のチップ間接属性能、チップレット集積規模の拡大といった要求を、最小限の構成と製造プロセスで実現する技術「Pillar-Suspended Bridge(PSB)」を開発したことを発表した。

同成果は、東工大 科学技術創成研究院 未来産業技術研究所の栗田洋一郎 特任教授、アオイ電子ほか4企業の共同研究チームによるもの。今回の研究の詳細は、現地時間10月6日まで米・ボストンで開催のマイクロエレクトロニクスの国際会議「IMAPS 2022」にて発表された。

「ムーアの法則」に代表される半導体の性能向上は、これまでプロセスの微細化がけん引してきたが、近年、数nmプロセスというレベルに達し、物理限界を迎えつつある。一方で、AIやHPCを中心に、コンピュータの性能向上は留まるところを知らず、微細化の代わりとなる集積化技術、性能向上技術、低消費電力化技術などの実現が求められるようになってきている。そうした中、それらを実現する技術の1つとしてチップレットに注目が集まっている。

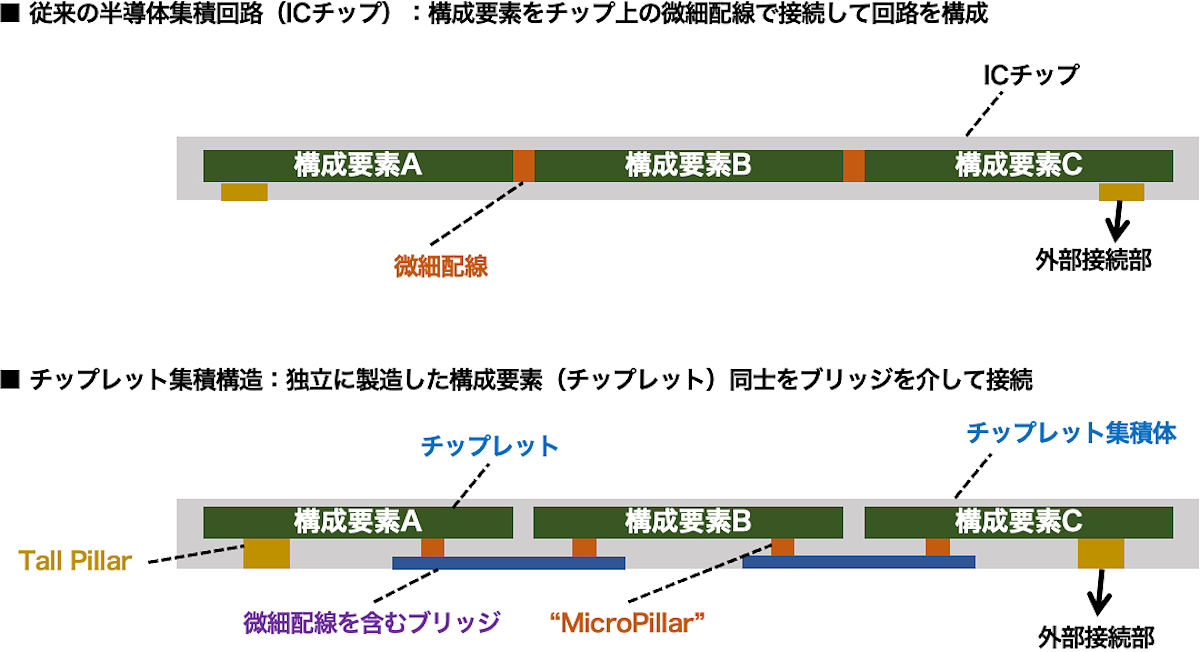

チップレットは、それぞれの機能を搭載した複数のチップを従来の半導体実装技術に比べて密に実装することで、1チップ上に異種チップを混載し、性能向上と低消費電力化の両立を可能とするもの。2.5Dや3D IC技術の1種として期待されている。そうしたチップレット集積のためのプラットフォーム技術は、これまでにいくつか開発・実用化されてきているものの、大規模な集積にはウェハサイズや製造技術による制限が指摘されていた。一方、シリコン・ブリッジという局所的に配置された高密度配線チップを用いる技術が大規模集積に向けて開発されているが、その構造や製造プロセスの複雑性や高集積化のための製造精度の高さが課題となっていたという。

そこで研究チームは今回、最小要素のチップレット集積構造/プロセスとしてPSB技術を考案し、コンセプト実証試作を行い、その実現性を立証してさまざまな課題克服を目指すことにしたという。