まだ重要な問題が1つ残っている。BPR集積、ウェハ薄化、nTSV形成などの新たに追加されたプロセスステップは、フロントエンドで製造されるデバイスの電気的性能に影響を与えるのではないかという疑問である。

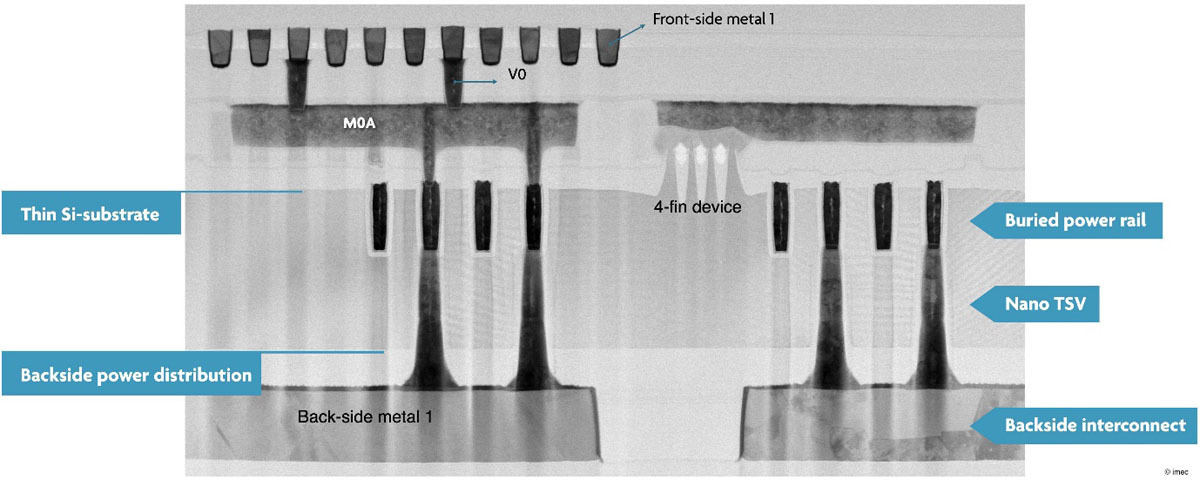

この質問に答えるために、imecは最近、製造フローと上記の改善されたプロセスステップを使用してテストツールを製作した。このテストツールでは、スケーリングされたFinFETが、BPRに着地する深さ320nmのnTSVを介して、厳密なオーバーレイ制御でウェハの裏面に接続される。 BPRは、M0A層とV0ビアを介して前面メタライゼーションにも接続する。とりわけ、この表面接続により、研究者は裏面プロセスの前後でデバイスの電気的性能を評価することができた。imecは、このテストツールを使用して、BPRの実装と裏面処理によってFinFETの性能が低下しないことを確認した。

裏面電源供給ネットワークの適用分野は?

いくつかの半導体メーカーは、2nm以降のテクノロジーノードのロジックICに裏面電源供給ネットワークを導入することを公表している。今こそ、ナノシートトランジスタの出番である。それにとどまらず、この新しい配線技術は、幅広いトランジスタアーキテクチャに使用できる。imecのロードマップは、6Tスタンダードセルのナノシートトランジスタを使用して、先進技術ノードでの導入を予測している。BPRと組み合わせることで、標準セルの高さを6T未満にすることができる。

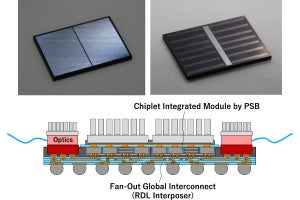

しかし、裏面電源供給ネットワークの応用分野は、2DシングルチップICだけにとどまらない。3Dシステム・オン・チップ(3D SoC)のパフォーマンス向上も約束されている。一部またはすべてのメモリが上部ダイに配置され、ロジックが下部ダイに配置される3D SoC実装を想像してみていただきたい。技術面では、これは「ロジックウェハ」のアクティブな表面を「メモリウェハ」のアクティブな表面に張り合わせることで実現できる。この構成では、両方のウェハの元の裏面が3D SoCシステムの外側に配置される。「ロジックウェハ」の「空いている」裏面を活用して、電力を大量に消費するコアロジック回路に電力を供給することが考えられる。これは、2D SoCで提案されているのと同じ方法で実現できる。主な違いは、ウェハの薄化を可能にするために以前に導入された元のダミーブランケットウェハが、2番目のアクティブなウェハ(この場合はメモリウェハ)に置き換えられるということである。

このような設計はまだ実験的に実装されてはいないが、IRドロップの観点からの最初の評価は非常に有望のものだった。提案されたソリューションは、先端ノードリサーチ・プロセス・デザイン・キット(PDK)を使用して、メモリ・オン・ロジック分割設計で検証された。

nTSVとBPRを使用した裏面電源供給ネットワークの実装は、有望な結果を示した。従来の表面からの電源供給と比較して、ボトムダイのIRドロップが平均で81%、ピークで77%減少した。これにより、先端CMOSノードでの3D ICの電源供給に裏面電源供給が理想的であることが証明された。

2Dおよび3D構造の両方で、ウェハ裏面の空きスペースを活用するという概念は、I/OやESDデバイスなどの特定のデバイスを裏面に追加することで、ウェハの空いている裏面を活用するという概念を他の機能に拡張できる可能性がある。

たとえば、imecは裏面プロセスと、デカップリングコンデンサとして機能する2.5D(つまり柱状)の金属 - 絶縁体 - 金属コンデンサ(MIMCAP)の実装を組み合わせた。 2.5D MIMPCAPは静電容量密度を4倍から5倍に高め、IRドロップをさらに改善する。結果は、実験データで調整されたIRドロップモデリングフレームワークから導き出された。

まとめ

将来のチップは、前面から電力を供給するという伝統を打ち破る可能性がでてきた。裏面金属配線、埋め込み電源レール、およびnTSVを備えた裏面電源供給ネットワークは、IRドロップの低減、BEOLにおける歪みの解放、および標準セルの高さスケーリング(比例縮小)の改善において明確な利点を示している。

BPR集積、ウェハボンディング、ウェハ薄化、nTSVプロセスなどの重要な製作工程は徐々に改善されており、先進ロジック テクノロジーノードや将来の3D SoCに導入する準備が始まっている。

|

Naoto Horiguchi

ベルギーimecのロジックCMOSスケーリングプログラムディレクター。 富士通研究所を経て2006年からimecで先端CMOS デバイスの研究に従事し、現在の興味は1nmテクノロジノードを超えた微細化 |

|

Eric Beyne

imecのR&D担当副社長、および3Dシステム統合のプログラムディレクター。1986年からimecで高度なパッケージングと相互接続技術は開発に取り組んでいる。 |

2022年10月21日訂正:記事初出時、執筆者の1人であるNaoto Horiguchi氏のお名前を掲載当初、Naoto Horiuchi氏と表記しておりましたので、当該箇所を修正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。