埋め込み電源レールとナノ貫通シリコンビアがカギ

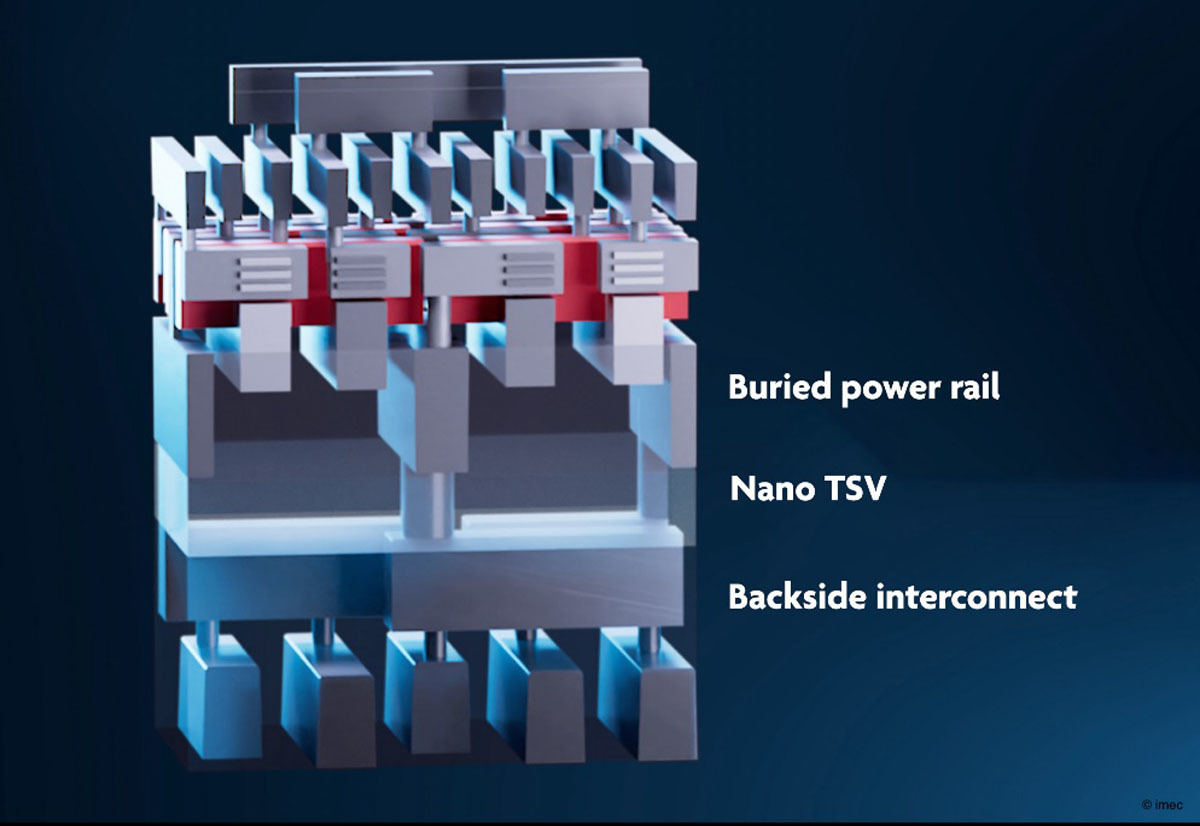

裏面電源供給ネットワーク(BSPDN)を形成するプロセスフローについて詳しく述べる前に、これを可能にする2つの重要な技術について紹介する。

それは、「埋め込み電源レール(Buried Power Rail:BPR)」と「ナノシリコン貫通ビア(nano-Through-Silicon Via:nTSV)である。

BPRは、標準セルの高さを比例縮小測にしたがいさらに低くし、IRドロップを低減する比例縮小技術のブースター(推進役)である。これは、トランジスタの下に埋め込まれた金属配線構造を指す。BPRは、シリコン基板内に部分的に配置された浅いトレンチ分離酸化膜で囲まれた溝に配置されている。これは、BEOLの標準セルレベルに従来実装されてきたVDDおよびVSS)の電源レールの役割を果たしている。

このBEOLからFEOLへの役割の歴史的な移行によりMintトラックの数を減らすことができ、標準セルをさらに縮小することが可能になる。さらに、レールを標準セルに対して垂直に設計すると、レールのサイズを緩和できるため、IRドロップがさらに減少する。

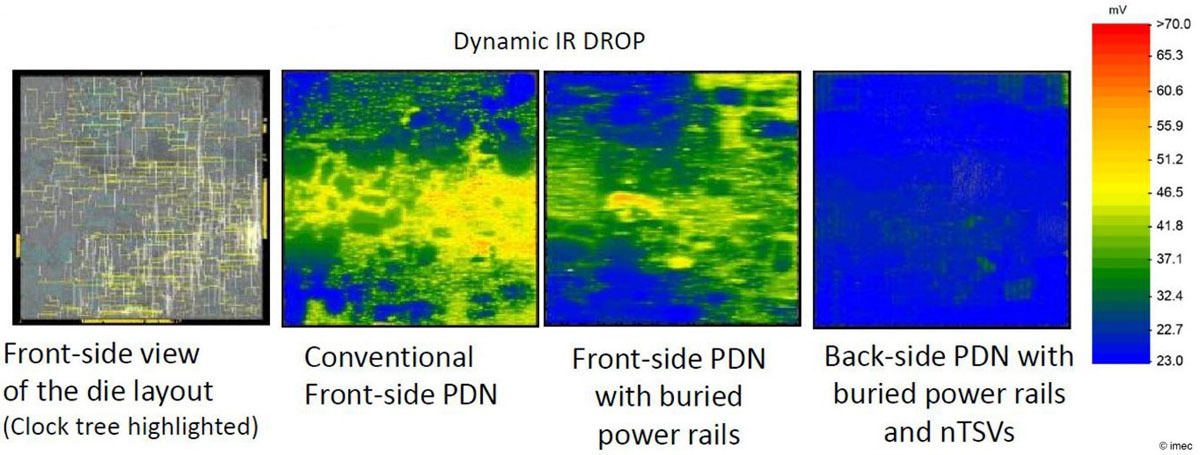

厚さが薄くなったウェハの裏面に形成された高アスペクト比のビアであるnTSVとBPRを組み合わせることで、BPRの潜在的な可能性を十分に引き出せる。これらを組み合わせることで、ウェハの裏側から表側のアクティブデバイスに、最も効率的な方法で電力を供給することができる。つまり、IRドロップの削減を最小化できる(図3参照)。

裏面電源供給方式の定量的評価

imecは、英Armと共同で、裏面電源供給方式の定量的評価を行い、その結果を2019年の国際電子デバイス会議(IEDM)の場で発表した。Armは、先端設計ルールで設計された中央処理装置(CPU)の1つを使って電力を供給する3つの方法をシミュレーションで比較した。

3つの方法とは、以下の通りである。

- 従来通りの表面側からの電源供給

- BPRと組み合わせた表面側からの電源供給

- BPRに接続したnTSVを使用した裏面電源供給

シミュレーションの結果、電源供給効率に関しては、最後の(3)が明らかに有利だった。オンチップパワーヒートマップ(チップ上の発熱分布図)は、(2)が、従来方式の(1)と比較して、IRドロップを最大1/1.7に削減できることを示した。しかし、裏面から電力を供給する(3)はさらに優れており、IRドロップを1/7に削減できた。

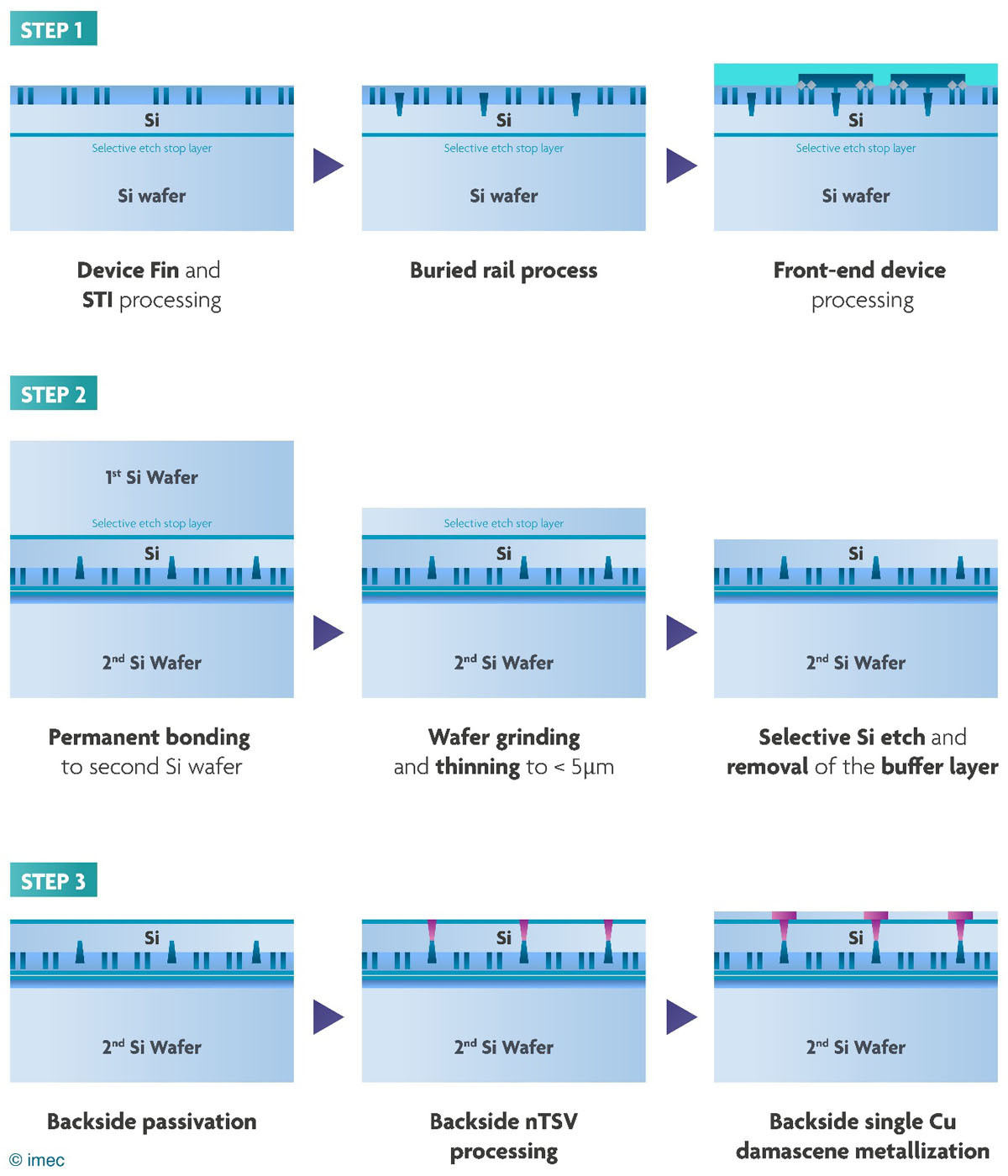

裏面電源供給ネットワーク形成:全体の流れ

BSPDN(裏面電源供給ネットワーク)を形成するためのプロセスフローの一例を以下に示す。この方法では、非常に薄いウェハの裏面に形成されたnTSVがBPRの上に配置される。ウェハの表面に形成された微細なFinFETなどのデバイスは、BPRとnTSVを介してウェハの裏面に接続される。

ステップ1:埋め込みレール形成のための表面プロセス

プロセスフローは、300mm Siウェハ上にSiGe層を成長させることから始まる。SiGe層は、後でウェハの厚みを薄くするためにエッチングする際、エッチングを停止するためのストップ層として機能する(ステップ2)。次に、 SiGe層の上に薄いSiキャッピング層を成長させる。これは、デバイスと埋め込み電源レールを形成するための出発点である。埋め込み電源レールは、浅いトレンチ分離後に形成する。Siキャッピング層にエッチングでトレンチを形成し、それを酸化物ライナーと金属、例えばWまたはRuで満たす。結果として得られる埋め込みレールは、通常、幅が約30nm、ピッチが約100nmである。次に、表面の金属は削りとられて、誘電体で覆われる。デバイス(この場合、スケーリングされたFinFET)の形成はBPRの形成後に完了し、BPRはVBPRビアとM0Aラインを介してトランジスタのソース/ドレイン領域に接続される。Cu配線形成により、ウェハ表面側のプロセスは完了する。

ステップ2:2枚のウェハ張り合わせとウェハの薄化

デバイスとBPRを形成されたウェハは裏返され、そのアクティブな前面がブランケットキャリアウェハに張り合わされる。これは、室温でのSiCN-to-SiCN誘電体融着と、それに続く250℃での接合後アニールを使用して達成される。次に、デバイスとBPRが形成された第1のウェハの裏面を、SiGeエッチストップが配置される場所まで薄くすることができる。薄型化は、裏面研削、CMPおよびドライおよびウェットエッチングステップを順次組み合わせることによって可能である。SiGe層は次のステップで除去され、ウェハはnTSV形成の準備が整う。

ステップ3:nTSV形成とBPRへの接続

一番目のウェハに裏面パッシベーション層を堆積した後、nTSVは、Si貫通アライメントリソグラフィプロセスによってウェハ裏面からパターン形成される。nTSVは、Si(深さ数100nm)を介してエッチングされ、BPRの先端に到達する。次に、nTSVに酸化物ライナーと金属(W)を充填する。nTSVは、標準セルの面積を消費することなく、200nmピッチで形成される。1つまたはいくつかの裏面金属層を形成し、nTSVを介してウェハの裏面を表面のBPRに電気的に接続することによってすべてのプロセスフローが完了する。

|

Naoto Horiguchi

ベルギーimecのロジックCMOSスケーリングプログラムディレクター。 富士通研究所を経て2006年からimecで先端CMOS デバイスの研究に従事し、現在の興味は1nmテクノロジノードを超えた微細化 |

|

Eric Beyne

imecのR&D担当副社長、および3Dシステム統合のプログラムディレクター。1986年からimecで高度なパッケージングと相互接続技術は開発に取り組んでいる。 |

2022年10月21日訂正:記事初出時、執筆者の1人であるNaoto Horiguchi氏のお名前を掲載当初、Naoto Horiuchi氏と表記しておりましたので、当該箇所を修正させていただきました。ご迷惑をお掛けした読者の皆様、ならびに関係各位に深くお詫び申し上げます。