2nm以降の先端ロジックデバイスをベルギーimecのパイロットラインで試作することを目指す欧州連合(EU)主導の「NanoICプロジェクト」が2月2日、2つのプロセス設計キットを発表した。

1つ目は高度なロジックスケーリングを実現するA14(いわゆる1.4nmプロセス)向けパスファインディングPDK(P-PDK)、もう1つは高度なメモリイノベーションを実現するeDRAMシステム探索PDKである。最先端の設計ルールとフローへの早期アクセスを提供し、ユーザーに高度なテクノロジノードと組み込みメモリの設計を提供するものだという。

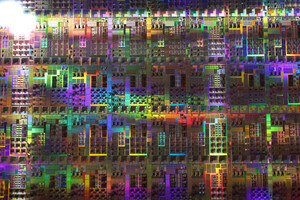

NanoICプロジェクトは、EUが制定した欧州CHIPS法のビジョンに基づき、imecに構築する2nm超の研究開発・試作ライン(既存のFab3および建設予定のFab4。量産はTSMCなどに委託予定)にてメンバー企業や大学、研究機関の先端半導体チップの試作受託を迅速に行い、欧州の先端半導体エコシステムの競争力を強化することを目的としたものである。

2つのPDKの特長

今回の2つのPDKの投入により、半導体設計者は、将来のコンピューティングシステムにとって重要な2つの技術分野、すなわち14Åプロセスでのロジックスケーリングと組み込みメモリの集積が可能になる。NanoICでは、これらのPDKを会員が自由に利用できるようにすることで、初期段階の設計検討と実際の物理的な集積を結び付け、現実的なスケーリング指標に基づいた設計を可能とすることを目指している。

例えば、A14 P-PDKは、次世代プロセスであるA14の探求に向けた仮想設計環境を提供するもの。Cadence Design SystemsとSynopsysがサポートしており、新たなスケーリングブースターであるダイレクトバックサイドコンタクトが導入されている。従来のN2(2nm)PDKではTSV-Middle(TSVM)構造によるバックサイド電力供給であったが、A14ではTSVMをよりコンパクトなダイレクトバックサイドコンタクト方式へと変更。ウェハ裏面からゲートに直接電力を供給することで、複雑な上面メタル配線を不要にしてIRドロップを削減し、等周波数およびセル密度においてN2比で18%の面積増加と7%の電力削減を実現するという。

一方のeDRAMシステム探索PDKは、高密度かつ低レイテンシのオンチップメモリ提供に向けたもので、高密度だが消費電力が大きいオフチップDRAMと、高速だが面積が限られたオンチップSRAMとの間のギャップを埋める組み込みメモリソリューションの探索に向けた仮想プラットフォームが提供される。

また、将来的には完全なシステム探索プラットフォームへと進化する予定で、次のフェーズではシステムレベルの相互作用全体を解析できるようになるとするほか、今後の開発ステップにはハードウェア検証が含まれ、最終的にはNanoICパイロットラインでのテープアウトと試作も可能になるという。

なお、これら2種類のPDKは、すでに提供済みのN2 PDKとともに欧州の大学や中小企業向けに、最先端の設計用CADや低コストのプロトタイピングサービスを提供する欧州連合傘下の組織であるEuropracticeを通じて入手が可能だという。