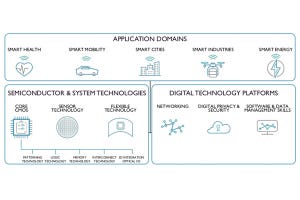

小規模な量子コンピュータの開発は日々進歩を遂げているが、大規模な量子コンピュータ用のデバイスアーキテクチャの設計は、なかなか進んでいない。効率的な量子アルゴリズムには、各量子ビットが隣接する量子ビットに接続され、外部回路やデバイスから簡単にアクセス可能な2D量子ビットアレイが必要である。しかし、量子ビットの数が増えれば増えるほど、その難易度は高くなってしまう。量子ビットをスケールアップする場合、配線図はますます複雑になってしまうということだ。

imecの量子コンピューティングプログラムマネージャーであるBogdan Govoreanu氏は、2Dバイリニアアレイで隣接するシリコン量子ビットを相互接続するスマートな方法(バイリニア2Dデバイス・アーキテクチャ)を2021年12月にサンフランシスコで開催されたIEDM2021で発表した。

コンパクトな設計で、スケールアップする際の主な制限の1つである量子ビットの接続性と配線のファンアウトの問題を解決したと主張している。このアーキテクチャは、半導体産業となじみの良いシリコンを用いて量子コンピュータを実現するための潜在的な道筋を示している。Govoreanu氏にこのアーキテクチャについて話を聞く機会をいただいた。

大型量子コンピュータを構築する方法は?

量子コンピュータは、量子物理学の性質を利用して、従来のコンピュータよりもはるかに高速に大量のデータを処理することができる。基本単位である量子ビットは、同時に2つの状態が存在するため、膨大な数の潜在的な結果を一度に選別することが可能である。

また、シリコンベースの量子ビットは、半導体業界で確立された大量生産プロセスと互換性があるため、量子コンピュータへの応用に適している。それにもかかわらず、量子ビットの数のスケールアップは、大規模な量子コンピュータを構築する上で障害となっている。小型のアレイは実証されているが、従来のコンピュータを凌駕する規模に拡張できる実用的な設計はまだ見つかっていない。

量子コンピュータの大型化のボトルネックは、量子ビットをどのように配置するかという問題である。効率的な量子アルゴリズムには、量子ビットが隣接する量子ビットと相互作用し、外部回路やデバイスからアクセスできる2Dアレイが必要である。各量子ビットは制御と読み出しのための専用線が必要で、2つの量子ビットの間には通常数10nmの小さな間隔が必要である。従って、量子ビットの数を増やすと、アレイの中心にある量子ビットにアクセスすることが困難になる。「シリコン量子ビットのバイリニア2D設計では、各量子ビットが他の4つの量子ビットに接続される。これは、この課題に対する洗練されたソリューションになりうる」とGovoreanu氏は述べている。

-

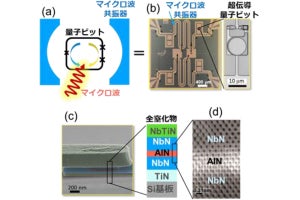

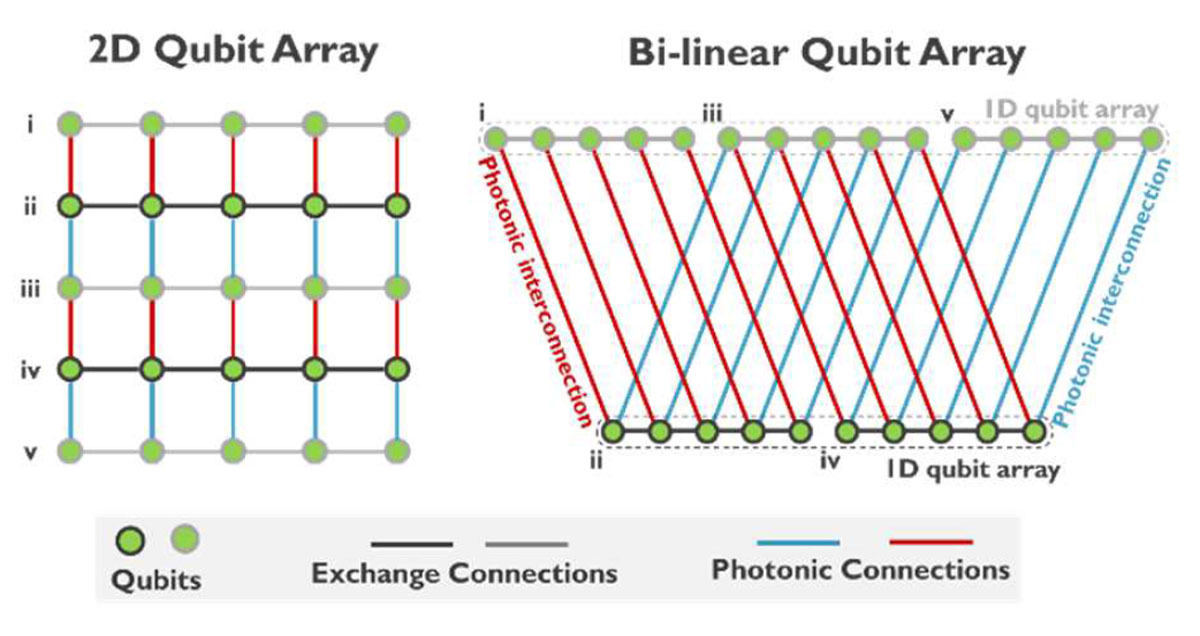

図1:正方形の2D格子から同等なバイリニアアレイへのマッピング。2つの1Dアレイに交互に配置された量子ビットの列。同じ1Dアレイ内の量子ビットは交換相互作用で結合され、1Dアレイ間は共振器によって結合されている(「フォトニック相互接続」) (出所:imec)

量子ビットの接続問題を解決するためには?

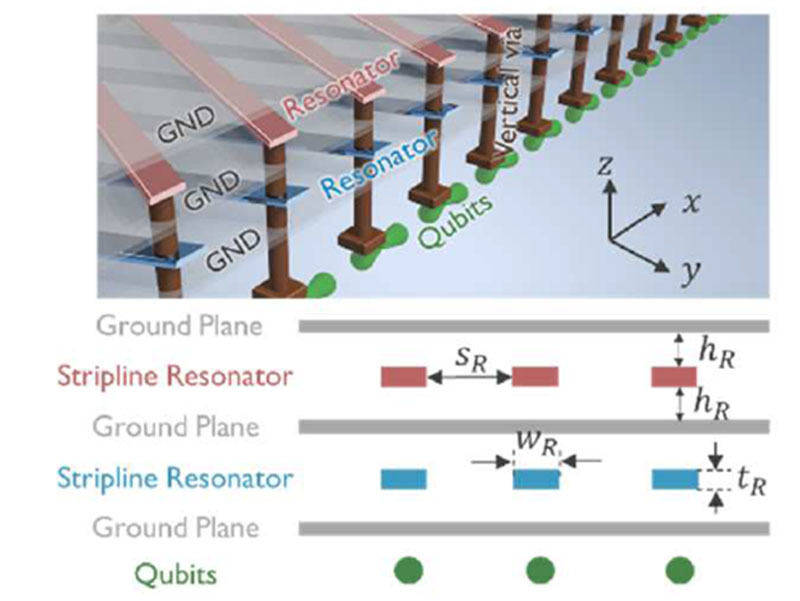

Govoreanu氏は、「2Dの正方形格子をトポロジカルにマッピングしなおして、いわゆるバイリニアデザインを形成する。このデザインでは、格子の交互の行を2行または1Dのアレイにシフトする(図1を参照)。2列に量子ビットを配置することで、等価な2D正方形格子配列の4つの接続を維持しながら、常にアドレス指定可能な状態を保つことができる。このアレイは、行に沿った1Dで成長させればよいので、拡張も容易である」、「2つの1Dアレイの間の接続は、2つの異なる平面で配線され、互いに分離するための接地平面で隔てられているため、交差しない(図2)」と説明している。

-

図2:1Dアレイ間の量子ビットを接続する共振器の模式図。共振器はグランドプレーン(接地平面)によって分離された別々の層に配置され、クロスオーバーを回避している。同じ層の共振器間のクロストークは、十分な間隔を確保することで最小化できる (出所:imec)

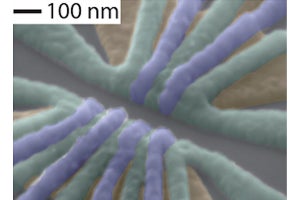

このアーキテクチャでは、各量子ビットが、量子ドットと言うポテンシャルの井戸に閉じ込められた電子のスピンの向きに対応している。この量子ビットを結合することで、「量子もつれ」が生じ、量子コンピュータの飛躍的な演算能力が実現される。

量子ビットのもつれは、それぞれの量子ビットがもつ量子状態のすべての可能な組み合わせを記憶する。1Dアレイ内の量子ドットは、近接する量子ドットの電子間のスピン相互作用によって結合される。近接する電子スピンは、交換結合と呼ばれる量子力学的プロセスによって自然に相互に作用する。1Dアレイ間の量子ドットは、超伝導材料を用いて製作されたマイクロ波共振器を介して長距離(~mm)結合される。このような長距離結合は、量子ビットの電子が2つの量子ドットの間で非局在化したときに、量子ビットの状態が共振器のフォトニックモードに結合できるために可能となる。

エラーに対する耐性は?

量子状態は非常に壊れやすく、誤りが発生しやすい状態である。そのため、大規模な量子コンピュータを構築するには、量子ビットの数を増やすだけでなく、誤りに対していかに耐性を持たせるかが重要になる。

量子コンピュータは、従来のコンピュータと同じ誤り解法アルゴリズムが使えないため、「論理量子ビット」による量子エラー解法技術に頼ることになる。論理量子ビットは、何千もの物理量子ビットを複雑に配列したもので、1つの量子ビットを符号化するために使用される。「私たちの設計は、広く受け入れられている量子誤り解法方式である表面コードと互換性があり、特定の量子ビットエラーにまで耐えうるアルゴリズムを実行できる」と、Bogdan Govoreanu氏は説明している。

「論理量子ビットを実装するための物理量子ビットの典型的な数は、物理量子ビットの品質にもよるが、103から104の間であると考えられている。実用的な大規模アルゴリズムの実行には、数百から数千の論理的量子ビットが必要であり、これは物理的量子ビットの総数が100万を超える可能性があることを意味している。IEDM2021では、量子エラー訂正に必要な量子リソースの特性を明らかにするとともに、必要なデバイス寸法、許容ノイズ仕様、量子ゲート動作時間について詳細に分析した結果が発表された(図3)。バイリニアアーキテクチャは、100万量子ビットのシステムでも36mm2程度の非常にコンパクトな量子論理面積しか占有しない。さらに、量子ドットを定義する共振器と静電ゲートは、バイリニアアレイの両側から容易にアクセスできるため、配線のファンアウトの複雑さが大幅に軽減される」。

「この設計は、現在のCMOS製造技術と互換性があり、将来の大規模シリコン量子コンピュータの実証に道を開くことができる」とGovoreanu氏は結論付けている。

・IEDM2021論文#27-5“Large-Scale 2D Spin-Based Quantum Processor with a Bi-Linear Architecture”