12月15日から17日にかけて東京ビッグサイトにて開催されている「SEMICON Japan 2021 Hybrid」にて、SEMIは特別企画として、量子コンピューティングの業界、技術、製品、企業を紹介する「第2回 量子コンピューティングパビリオン」を提供している。

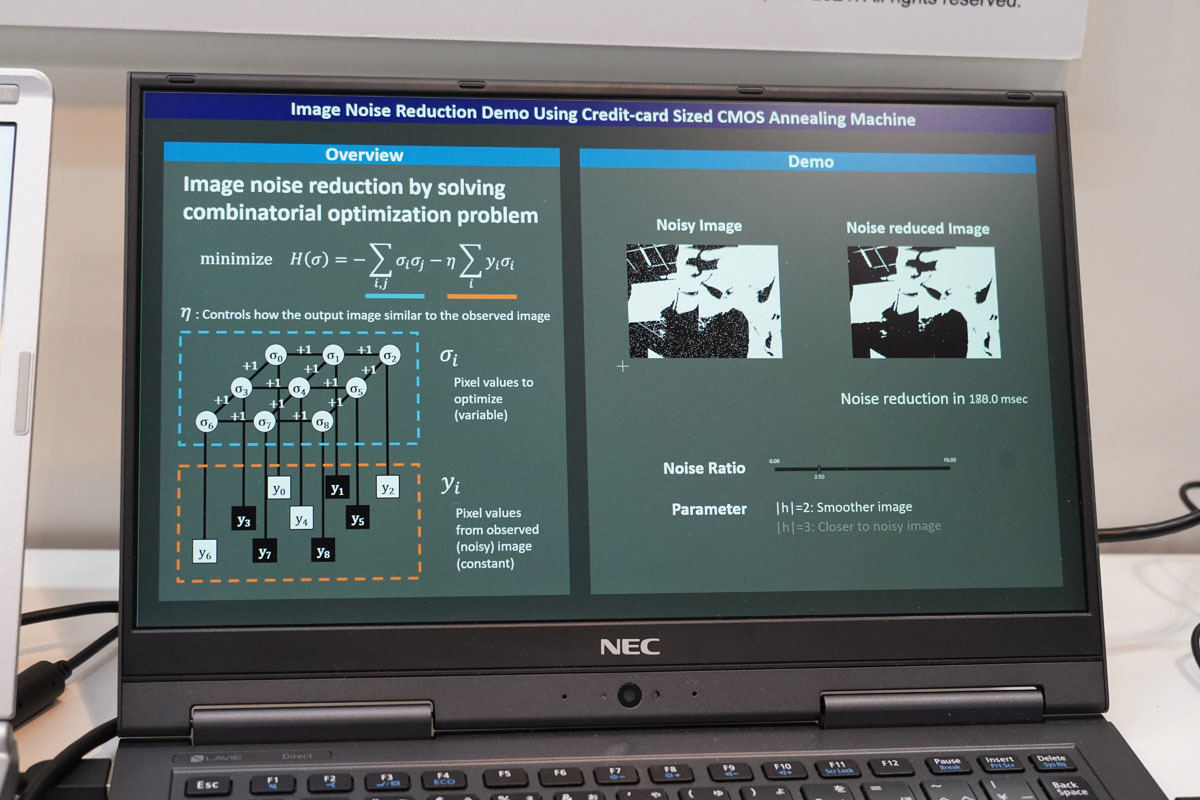

同パビリオンの出展者は産業技術総合研究所、JSR、日立製作所、blueqatの4者。このうち、日立では、名刺サイズのCMOSアニーリングマシンのプロトタイプを用いたWebカメラで撮影したリアルタイム映像のノイズ除去デモを行っている。

同社ではCMOSアニーリングとして、GPUを用いたMomentum Annealing(MA)アルゴリズムと、ASIC/FPGAを用いたSimulated Annealing(SA)アルゴリズムの2種類を実装。サービスとしてはハードウェアを提供するのではなく、顧客からの案件を受け取って、日立でこれらの処理を行い、その結果を渡す、といった流れとなるという。すでにシフト作製ソリューションなどが提供されているという。

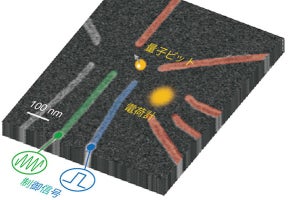

名刺サイズのCMOSアニーリングマシンのプロトタイプを用いたデモの様子。基板右側の2つのチップが30kスピンに対応したチップ×2で、60kの最適化問題を処理できる。今回はノイズ除去に特化したASICとして構成されたものでデモを実施しているという

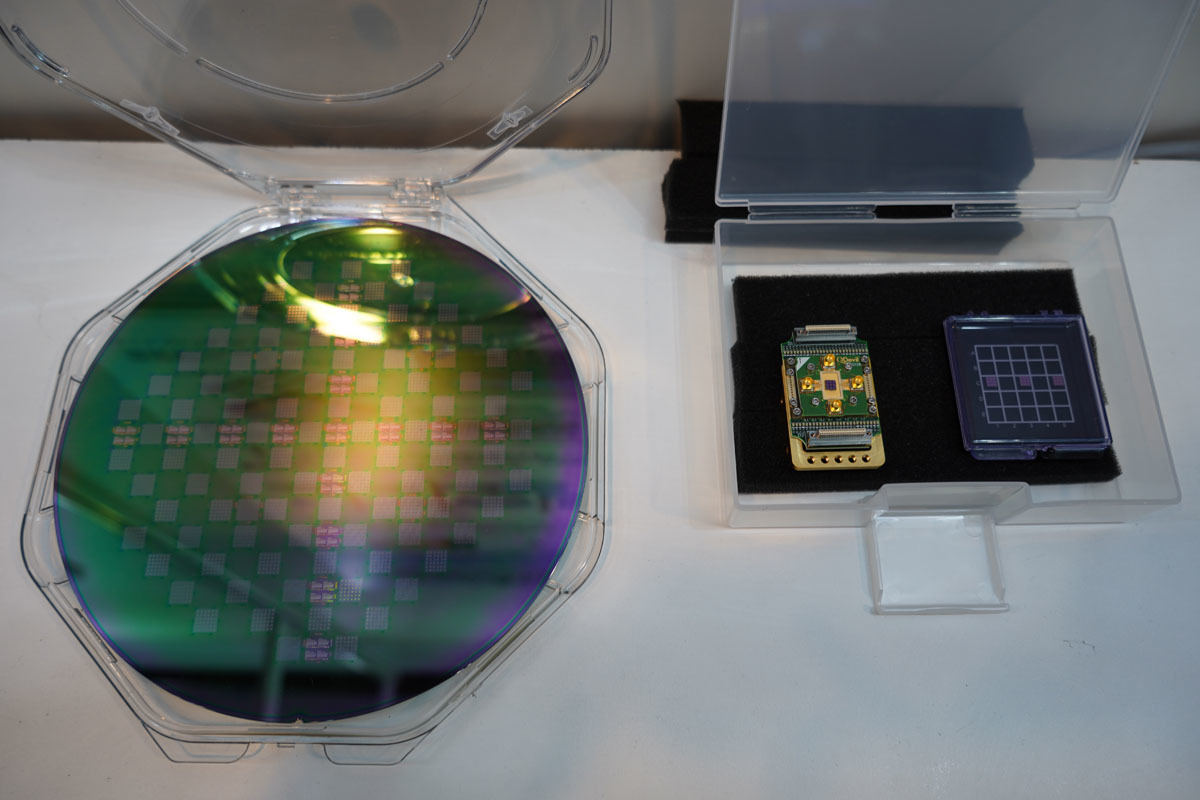

また、現在開発中のシリコン量子コンピュータの実現に向けた開発中のシリコン量子ウェハの展示も行われている。

これは量子ドットアレイを中心に、量子ドットを制御するデコーダ/セレクタ回路などをCMOSプロセスで周辺に構築するというQ-CMOSプロセスの実現に向けた研究として進められているもの。回路としてはメモリ技術を応用する方向で考えられており、最終的な0と1の判定には量子スピンを用いることが想定されているが、現段階では、実際に量子ビットが動作しているかどうかをさまざまな条件で検証を進めているという初期も初期の段階とのことで、2030年代での実現に向け、各所と協力して研究開発を進めていくとしている。