Micron Technologyはオンライン開催となったCOMPUTEX TAIPEI 2021で、6月2日の10:00(台北時間)より同社CEOであるSanjay Mehrotra氏の基調講演、同じ2日の17:00(台北時間)よりRaj Hazra氏(SVP&GM, Computer&Networking Business Unit)による「Memory at the Heart of AI Innovation」と題した講演を行う。この基調講演において同社が発表の内容が事前説明の形で紹介されたので、ご紹介したい。

176層NAND採用SSDと1αnm DRAM採用のDDR4

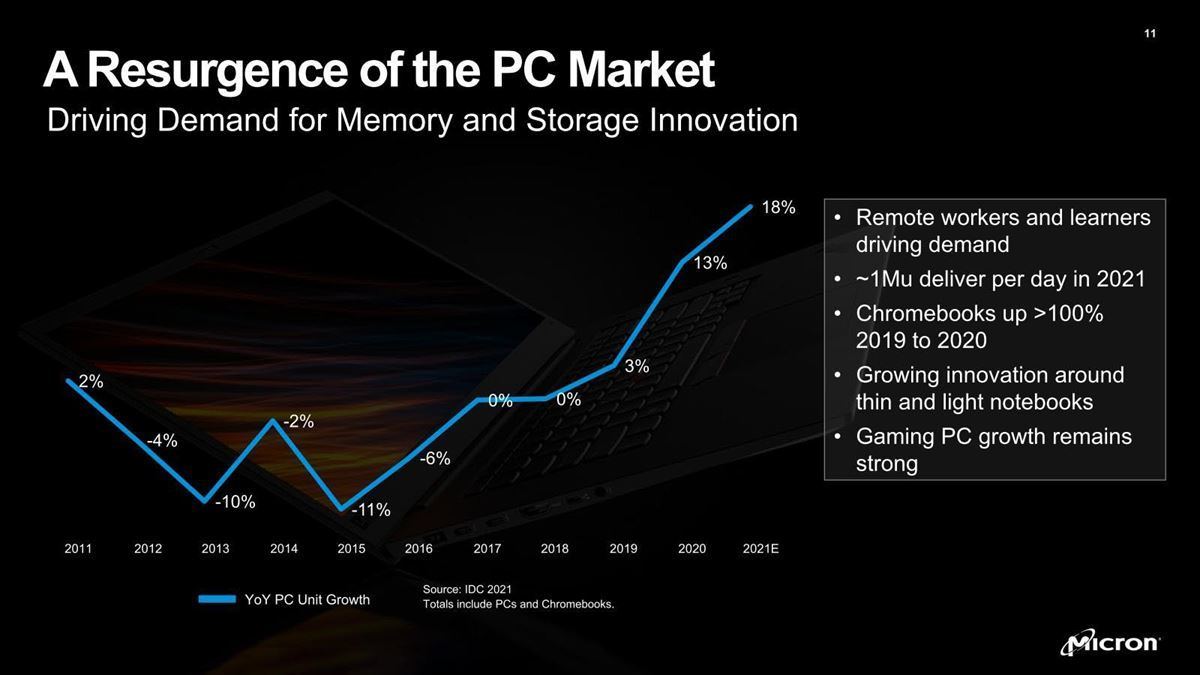

IDCのデータによれば、一時期は停滞していたPC Marketが、2019年から急速に伸びる状況になっている(Photo01)。

もちろん主要因はCOVID-19であるのだが、結果的にPost-Pandemic、あるいはNew Normalといった呼び方で新しい仕事の仕方やライフスタイルが定着し始め、ここにPCが必要という形になったことと、2019年あたりからGaming PCのマーケットが急速に伸び始めた事がその主な要因である。

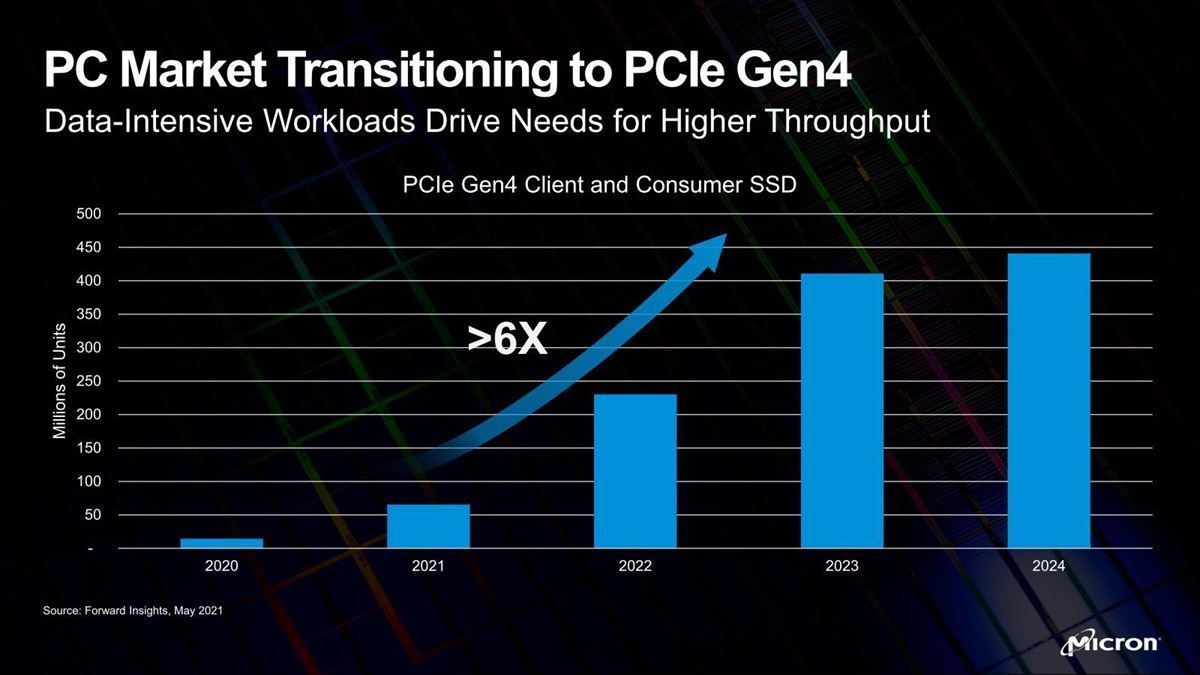

そのPC Market、急速にStorageがPCIe Gen4に移行を始めている。特に今年に入ってIntelがTiger LakeやRocket LakeなどのPCIe Gen4対応新プラットフォームを投入。それもあってSSDマーケットが急速にGen3→Gen4への移行を開始した。今後、PCIe Gen4対応SSDのマーケットは現在の6倍まで増える、としている(Photo02)。

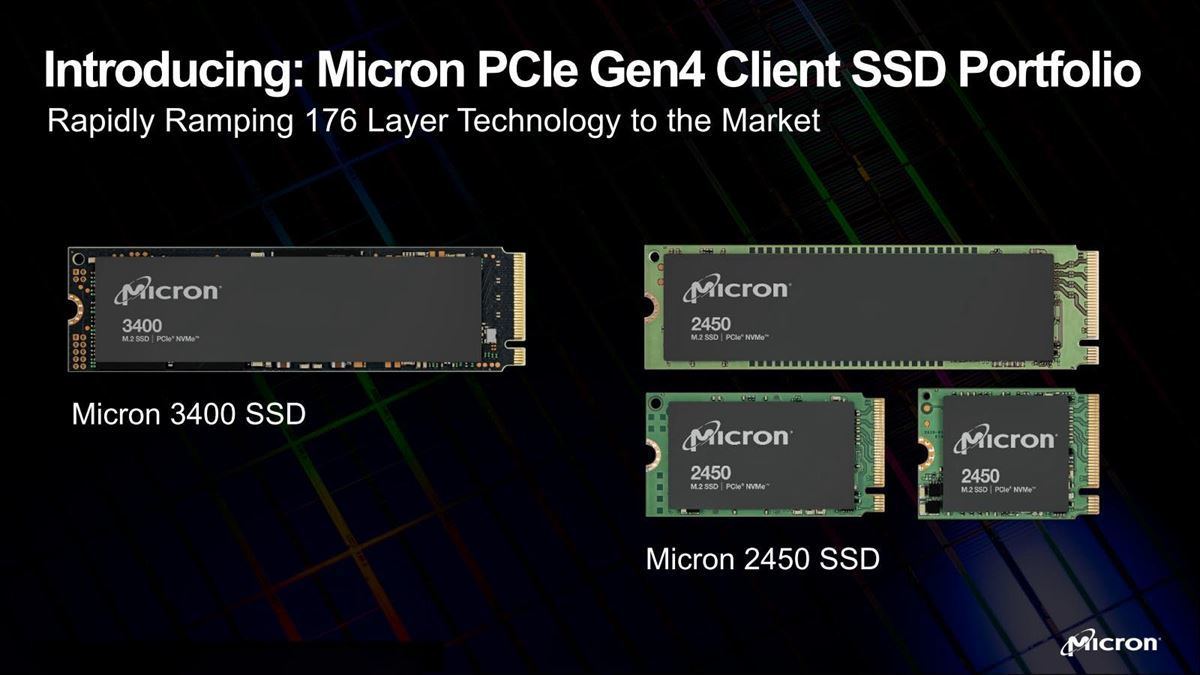

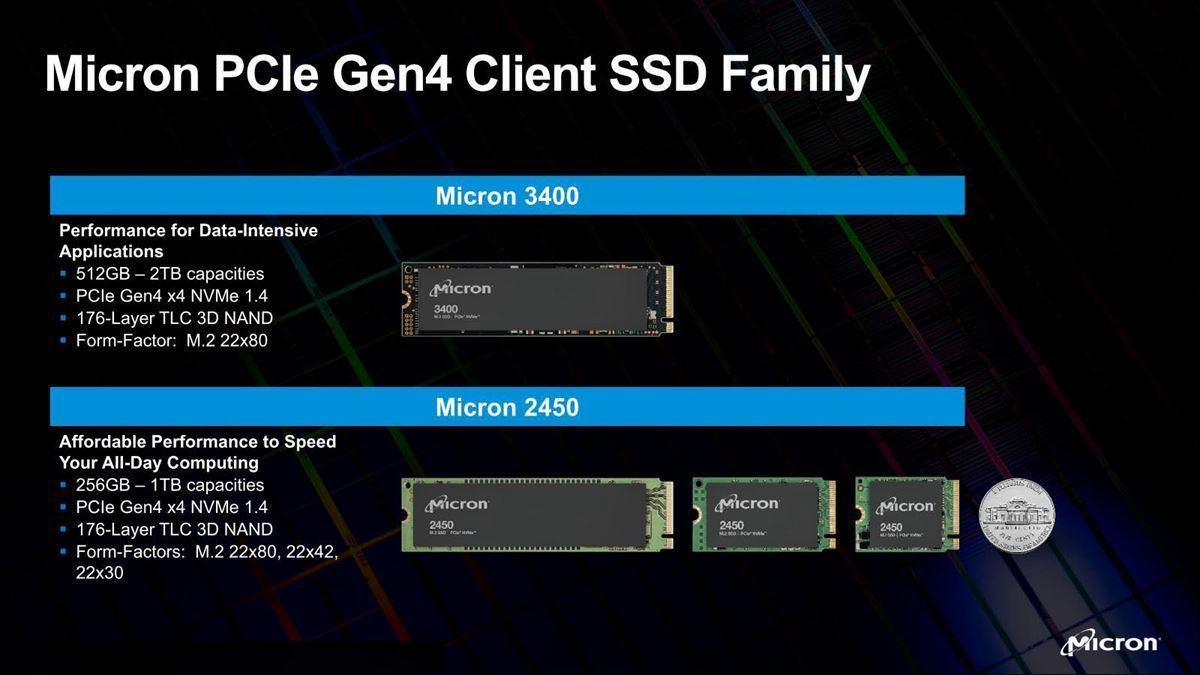

そこでMicronもここに向けて3400シリーズおよび2450シリーズのSSDを投入を発表した。いずれもPCIe Gen4対応となっており、3400シリーズは従来製品と比較して読み取りスループットが2倍、書き込みスループットが最大85%向上するとしている。

Photo04がもう少し詳細なスペックであり、いずれも同社の176層TLC 3D NAND Flashを採用している。

余談だが、すでにPCIe Gen5のプラットフォームの登場が予定されており、Marvellは業界初のPCIe Gen5 SSDコントローラを発表したという状況であり、それもあってPCIe Gen5への移行プランは? とJeremy Werner氏(CVP&GM, Storage Business Unit)にうかがったところ「PCIe Gen5は、むしろCXLを利用したMemory PoolとかStorage Poolの接続が先行する気がするが、ただ当然Consumerに降りてくるタイミングに合わせて我々もSSD向けSolutionを用意するが、それがいつになるかは現時点では言えない」との事であった。

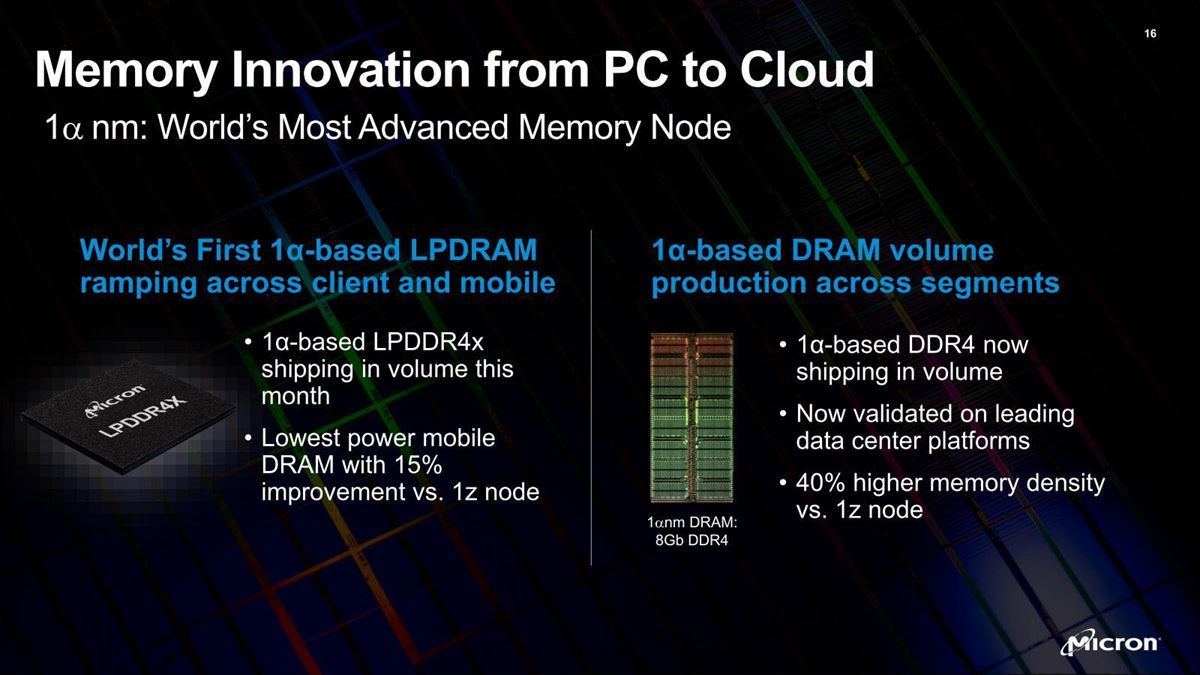

次いで1αnm DRAMについて。今年1月にMicronは176層3D NANDと併せて1αnmを利用したDRAMの量産開始をアナウンスしたが、LPDDR4とDDR4の両方に向けて順調に出荷量が増えているとする(Photo05)。

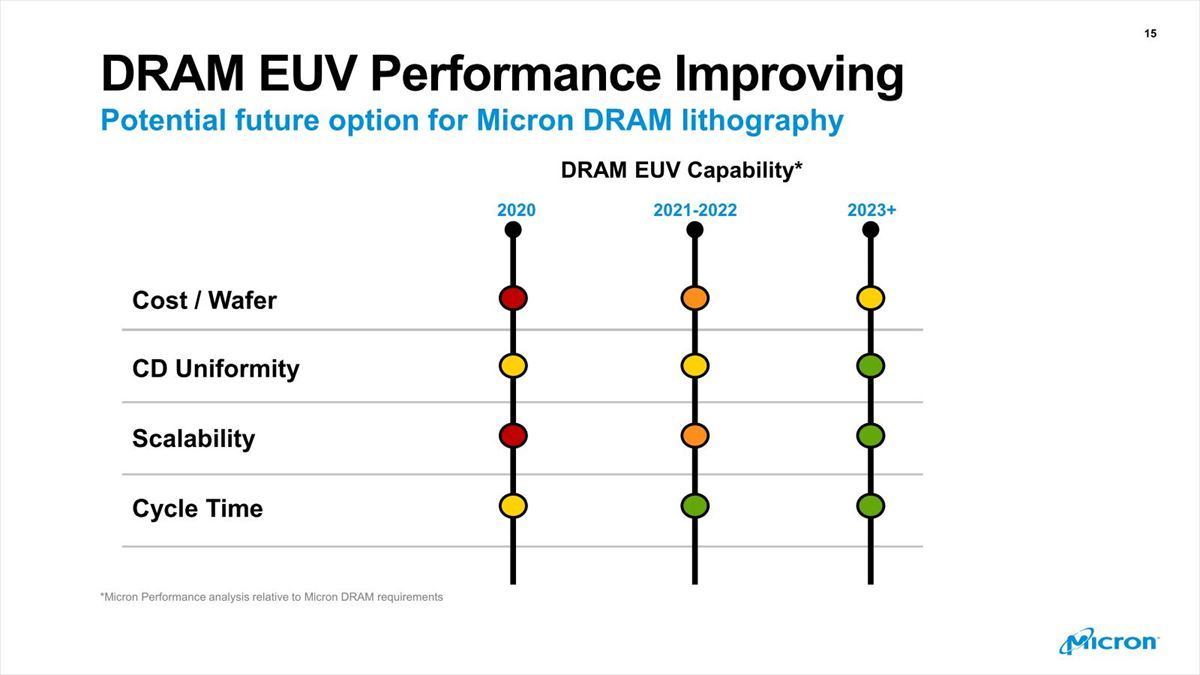

余談だが、この1αnmはまだ液浸ArFのダブルパターニング(SADP)が主体である。ただ次の1βnmはクアッドパターニング(SAQP)を利用する比率が多くなりそうで、EUVはさらにその先とみられている。同社が昨年11月に行ったTechnology Briefingにおける資料(Photo06)では、EUVが現実的に利用可能になる条件が揃うのは2023年以降になるという見通しであった。

-

Photo06:この時点では1αnmがCustomer Qualification、1βnmがEarly Development、1γnmがEarly Process Integrationで1δnmがPathfindingと説明されていた。で、EUVはこの1δnmの要素として説明されている

DDR5 Enablementと今後の展望

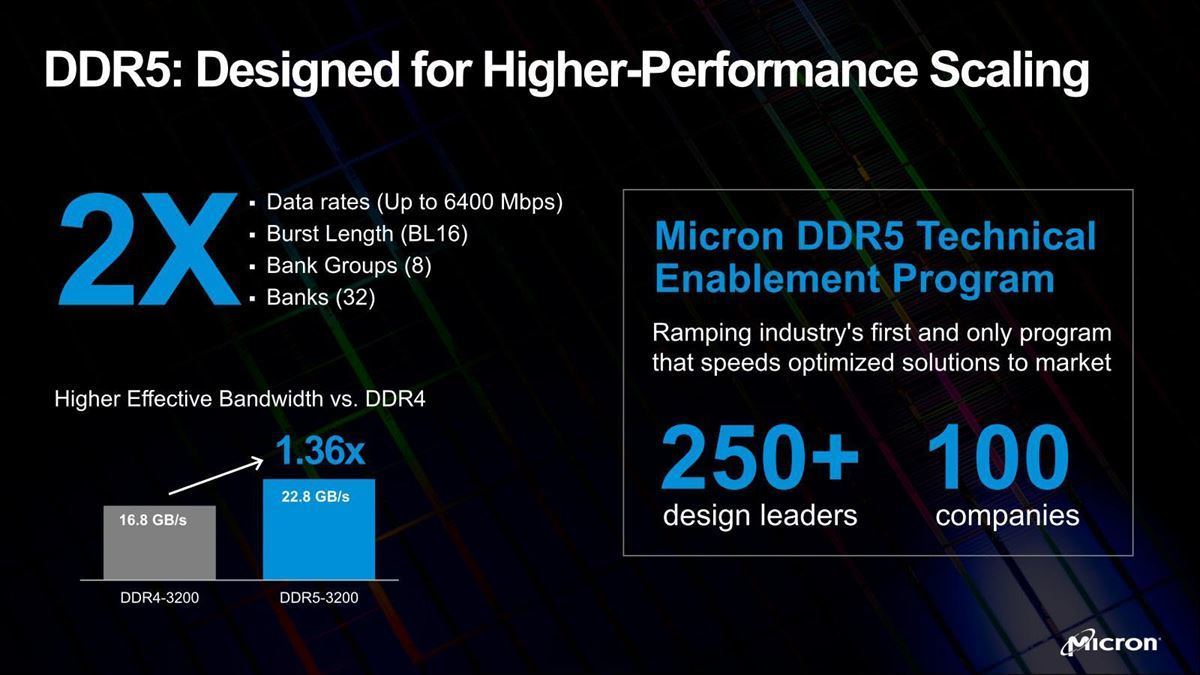

そのDDR4に採用されている1αnm DRAMを利用してMicronの最初のDDR5製品は製造される予定である。DDR5は単に動作周波数を引き上げたのみならず、バンク数やバースト長の増加、REFsb(Same-bank Refresh)、エラー訂正強化など多くの新技術が搭載されており、この結果として転送速度が同じであっても実効転送速度が向上する(Photo07)といったメリットがある。

-

Photo07:DDR5の場合、Single Rankの場合で64Bank/16 Group、Dual Rankで128Bank/32 Groupが利用可能(DDR4は32Bank/8 Group)で、バンク切り替えを効果的にりようすることでSIngle Rankで28%、Dual Rankで36%の実効帯域向上が期待できるとする

このDDR5への移行を進めるためにMicronが2020年7月から行っているのがDDR5 Technical Enablement Programで、日本を含む全世界で行われている。

ちなみに日本においてはAvnetがこのDDR5 Technical Enablement Programの代理店を行っている。このあたりの情報はこちらにまとまっているので、興味お持ちの方はご覧いただければと思う。

話を戻すと、このDDR5は先に出てきた176層3D TLC NANDと併せてMicronのEnterprise向け戦略の骨幹を成すコンポーネントの1つである(Photo08)。

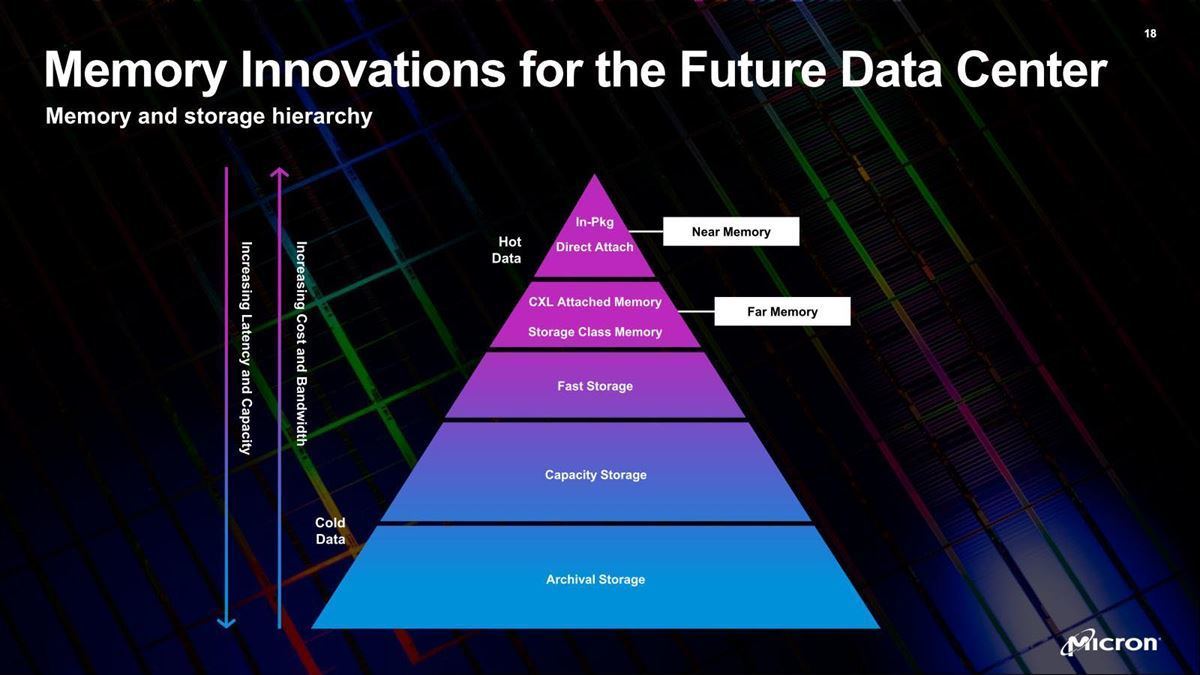

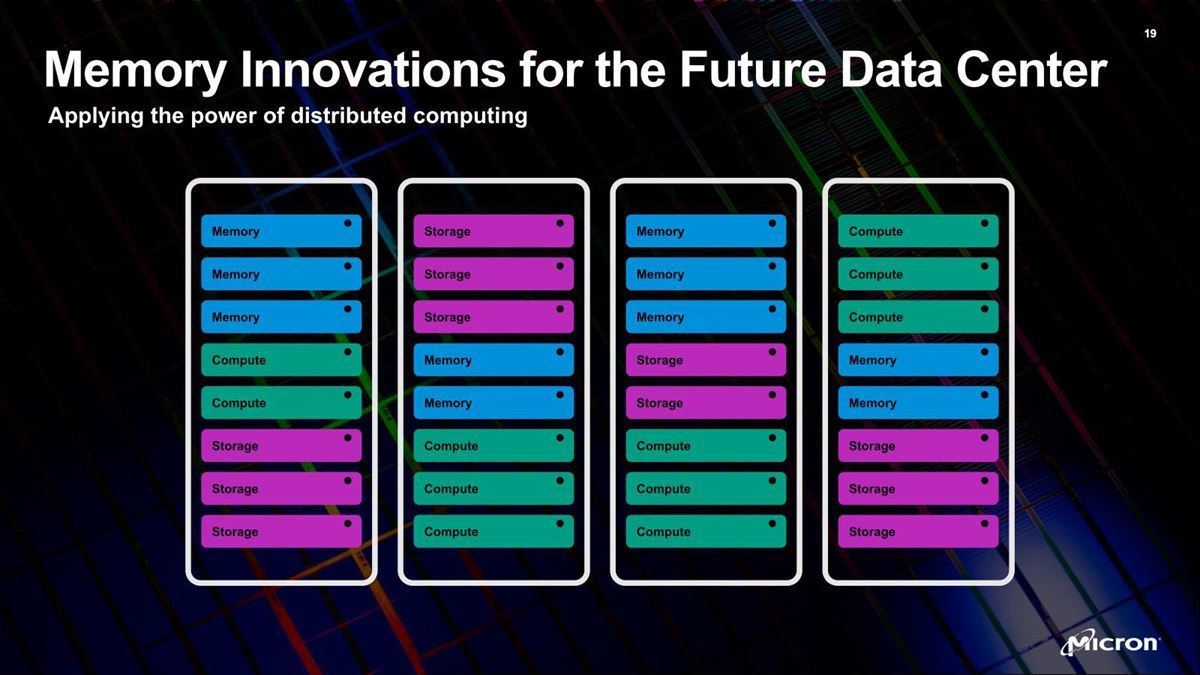

Micronは今年3月、Intelと共同開発していた3D XPointから完全に撤退し、その経営資源をCXLベースのMemory/Storageに注力する事を発表してい。なので今後同社はDDR5ベースのCXL Attached Memoryとか3D TLC NANDベースのCXL Attached Storage製品の実用化を急ぐとみられる。CXLを利用することで、将来のデータセンターはCompute、Memory、Storageが別々に提供され、これを必要に応じてオンデマンドに使うという「ある種の夢」がやっと現実になろうとしており、Micronはこのマーケットに今後も注力することを明らかにした。

-

Photo09:これ、古い話だが2013年にIntelがRack Scale Architectureとして示した図と大して変わらない。2013年当時は不可能だったことが、やっと現実的になってきたというべきか

車載向けUFS 3.1 Storage

最後が車載向けの話。昨今の自動車が高度に電子化が進んでおり、この結果として流れるデータ量も大幅に増加している(Photo10)。

-

Photo10:Connected CarとかEnrich cabinの様な判りやすい話以外にも、Car Shareingなどによるモニタリングや、自動運転に絡んださまざまや、そもそも車内のコンポーネントにセンサが大量に入る様になった事など、すべてが関係してくる

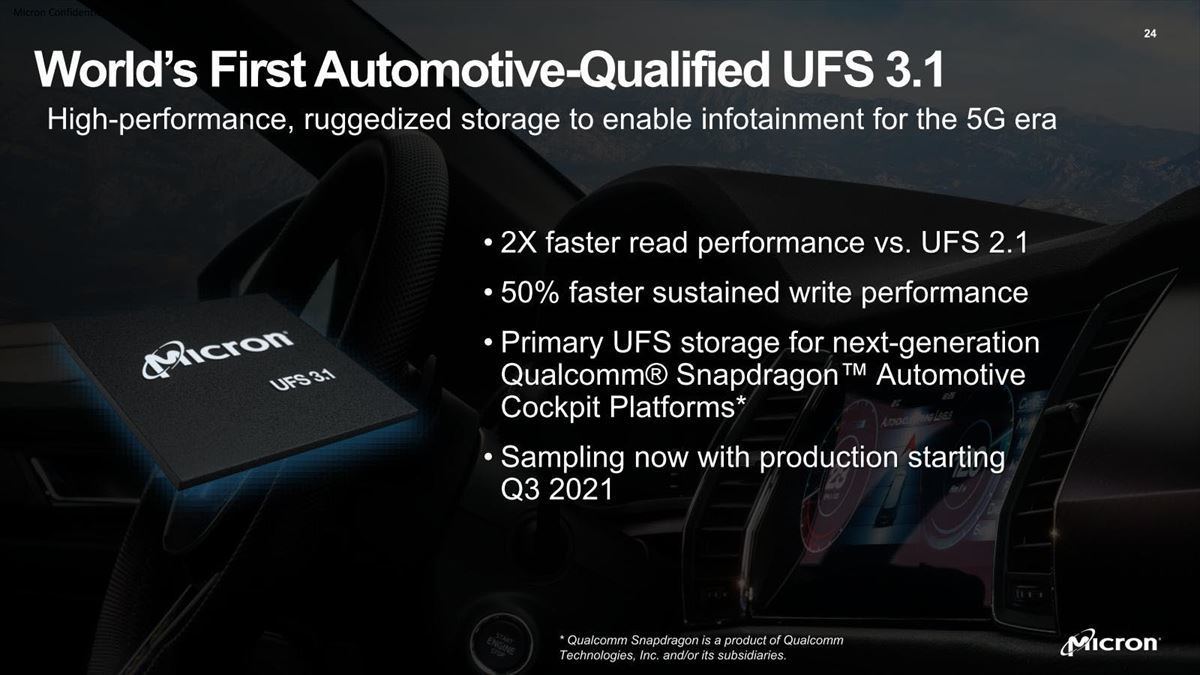

データ量が増加するという事は、より高速かつ大容量のストレージが必然的に必要になるということである。Micronは昨年、UFS 3.1 StorageにLPDDR5を組み合わせたスマートフォン向け製品を発表しているが、今回は次世代のSnapdragon Automotive Cockpit Platform向けに車載グレードのUFS 3.1 Storageを提供することを明らかにした(Photo11)。

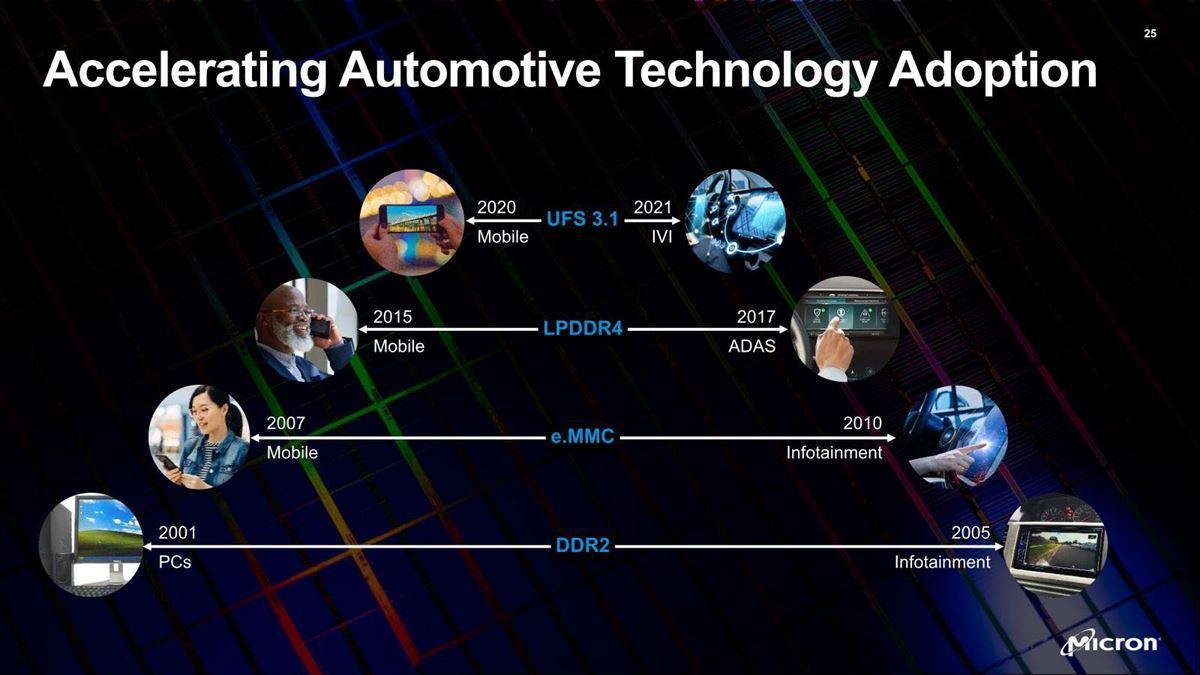

同社は民生向けと車載向けを、歩調をあわせて提供してゆくとしており、今回もその流れに沿ったものということになる(Photo12)。

ちなみにこの車載向けUFS 3.1 Storage、現在はサンプル出荷中であるが、第3四半期には量産出荷を開始するとの事である。