低コスト・高密度のDRAMへの需要はこれまでになく高まっている。IoT、自動運転車、5G通信などの登場でデバイスの数とデータ量が急激に増え、エッジおよびクラウドコンピューティングのインフラがさらにひっ迫しつつあるからだ。IoTデバイスは2030年までに5,000億個、そこから生成されるデータは年間1ヨタ(1024)バイトに達する見通しだ。

データは、処理されて初めて価値が生まれるが、AIの活用で実効性のある洞察を得れば、さらにデータの価値は上がる。それには安価で高性能なDRAMが大量に必要となる。DRAMメーカー各社は、DRAMの性能、消費電力、面積あたりコストを妨げるさまざまな物理的制約を克服しようとしのぎを削っているところだ。

そこで、キャパシタ(コンデンサ)と周辺回路のさらなるスケーリングに関する課題と機会について考えてみたいと思う。

DRAMのメモリセル構造

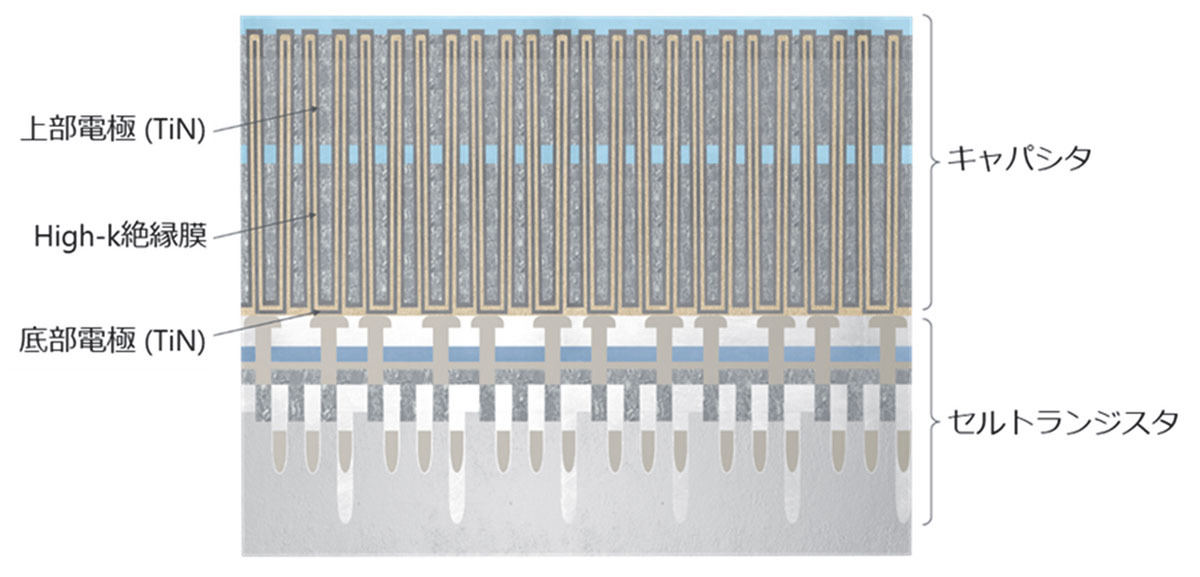

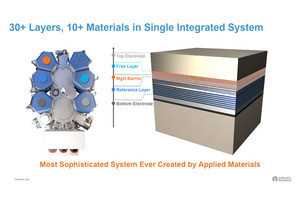

DRAMのメモリセルはトランジスタとキャパシタで構成されており、記録密度を高めるにはその両方のスケーリングが必要である。キャパシタは電荷を蓄えるもので、金属層の間に絶縁体層を挟む構造を用いている。

深い細孔の内壁は、窒化チタン(TiN)などの金属で被覆して底部電極が設けられ、その上に薄いHigh-K絶縁膜を形成し、最後に第2の金属層を形成する(図1)。

キャパシタアスペクト比のスケーリング

ストレージキャパシタに蓄積される電荷の量は、深いキャパシタ孔の内側と外側の表面積に比例する。キャパシタ孔の高さと直径の比をアスペクト比という。

メモリセルの二次元スケーリングでは直径が縮小するので、表面積と電荷を維持するためにアスペクト比を大きくする必要がある。二次元スケーリングを継続するためにキャパシタ孔の径を狭めていくので、アスペクト比を極端に高めるしかなくなる。

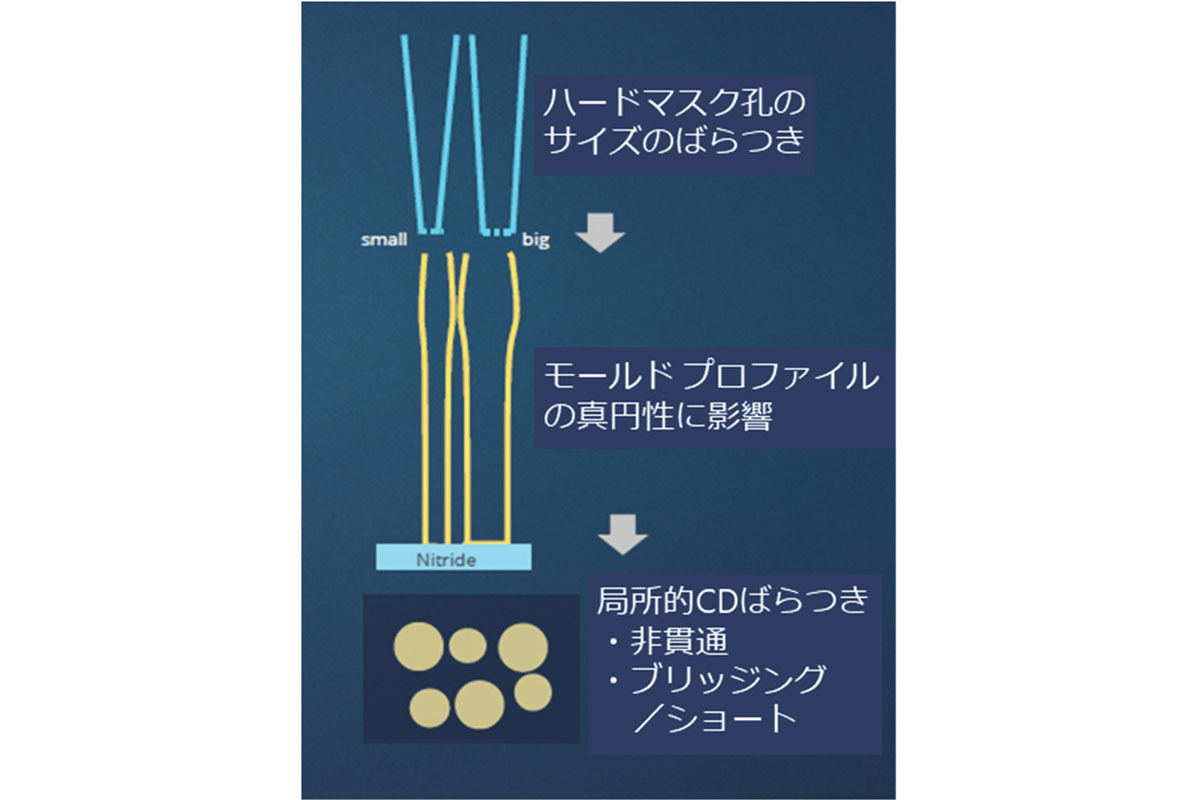

この手法はアイデアとして実用性はあるが、従来のパターニング技術では物理的限界に達している。具体的に説明しよう。キャパシタ孔は、アモルファスポリシリコンのハードマスク犠牲層で位置が決められ、エッチングでパターンが型抜きされる。

次にこれをステンシルマスクとして、下の厚いモールドをさらにエッチングすることで微細なキャパシタ孔が形成される。

高エネルギーイオンがキャパシタ孔をエッチングするが、同時にハードマスクもエッチングされる。アスペクト比が高いほど、キャパシタ孔が完全に形成される前にハードマスク材料がエッチングされ消失するリスクが大きくなり、チップが台無しになる。

このリスクに対応する方法の1つとして、ハードマスクを厚くすることも考えられるが、そうすると別の問題が生じる。ハードマスクの高さにキャパシタの孔径の狭さが加わるので、アスペクト比はいっそう高くなり、エッチングの完遂と副生成物の除去がますます困難になるのだ。残留したエッチング副生成物は、孔の曲がりやねじれ、エッチング不足、その他の物理的欠陥を招くこともある(図2)。

DRAMメーカーがスケーリングを継続するために最も必要としているのは、より高密度で固いマスク材料である。しかも、浸食速度はキャパシタモールド基板よりはるかに遅くなければならない。

そうした薄いハードマスクはより深いエッチングと副生成物の確実な除去を可能にし、まっすぐで深さが均一な正円柱形のキャパシタ孔の形成を実現する。

周辺回路のスケーリング

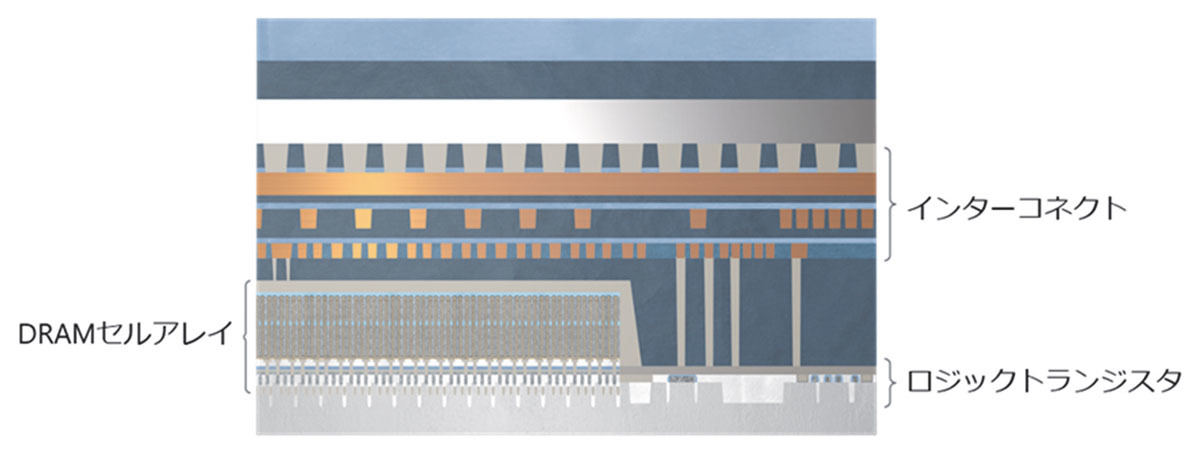

DRAMスケーリングを推し進める第2の方法は、周辺回路エリアのサイズを縮小することだ。周辺回路エリアはDRAMセルアレイを囲むエリアを指し、ロジックトランジスタと配線で構成される(図3)。

メモリセルだけをスケーリングして周辺回路が変わらなければ、ダイサイズに占める周辺回路エリアの割合が増える結果になる。ロジックの重要性は言うまでもない。現在の高速DDR4や新しいDDR5規格DRAMの性能と消費電力は、ロジックに大きく依存している。

ロジックトランジスタをセルエリアと接続する金属配線は、どれも絶縁材料で覆われ、電気信号の干渉を防いでいる。この絶縁体の厚さも、スケーリングに影響を及ぼす重要なファクターだ。DRAMメーカーはこの25年間、絶縁材料にシランないしテトラエトキシシラン(TEOS)のいずれかのシリコン酸化物を用いてきた。

今日、DRAMメーカーは、ロジックメーカーが20年ほど前に直面したのと同じ絶縁体スケーリングの課題に直面している。配線層間膜が薄くなりすぎると、金属配線同士が近接して容量性カップリングが増大するのだ。その結果、デバイスの消費電力増や性能低下、発熱増大、信頼性低下などの問題が生じかねない。

ロジックのスケーリングでは、銅とLow-k膜の新しい配線を採用することで、この問題を解決した。DRAMでも今、金属配線同士をより近く配置しながら信号の干渉を回避できる新しいマテリアルが求められている。

新しいマテリアルの研究

DRAMスケーリングに伴うマテリアルズ エンジニアリングの課題は、パターニング用ハードマスクと誘電性絶縁体の両方に係わるもので、集中的に研究が進められてきた。

後編となる次回はApplied Materialsが開発してきた新しいマテリアルについて取り上げる。これによりDRAM メーカーは製品ロードマップを前進させて、低コストで高性能なDRAMに対する需要の増加に応えることができると考えている。

著者プロフィール

Sony VargheseApplied Materials(AMAT)

セミコンダクタプロダクトグループ メモリ戦略マーケティング部門ディレクター

メモリ分野において今後鍵となる技術転換の課題を特定する業務に従事。

AMAT入社以前はMicron Technologyの研究開発部門で、メモリ技術の開発を担当。

申請中のものも含め、20以の半導体プロセスとインテグレーションに関する米国特許を保有する。

インド国立工業大学 スラスカル校で材料工学の修士号、オクラホマ州立大学で機械・材料工学の博士号を取得。