富士通研究所は11月27日、仮想環境におけるネットワーク処理の主要機能である仮想ルーターを高速化する技術を開発したことを発表した。

開発したのは、仮想ルーター機能をFPGAにオフロードし処理することで、CPUの処理を肩代わりするとともに、性能ボトルネックであったパケットの宛先制御を高速化する技術。

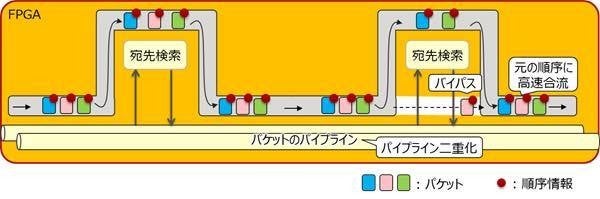

パケットのパイプライン上でパケットと別に順序情報を保持し、多段にわたる宛先検索処理において、前段検索の結果から不要となった次段検索をバイパスさせて合流させる際に、パケットのパイプラインの順序情報をもとに高速にパケットを元の順序に戻す。

これにより、高速なパイプライン処理を維持しつつメモリアクセスを低減させるとともに、パイプライン処理を二重化することでパケット処理性能を向上させるという。

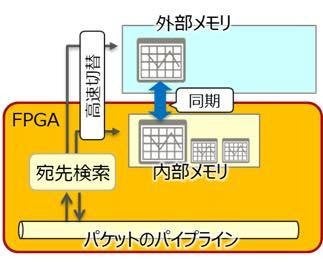

また、高速で小容量なFPGAの内部メモリと大容量の外部メモリとを、宛先検索処理を止めずに自動的に切り替える機能もあわせて開発した。

検索テーブル群のメモリ使用量が増え内部メモリの空き容量が少なくなった場合に、アクセス頻度が低い検索テーブルをバックグラウンドで外部メモリに同期しておき、検索処理を止めることなく外部メモリの検索テーブルに自動で切り替えるという。

これにより、大規模システムにおいて通信先が多く、大きな検索テーブルが必要な場合でも、外部メモリへのアクセスを抑えて、安定したパケット処理性能を実現するということだ。

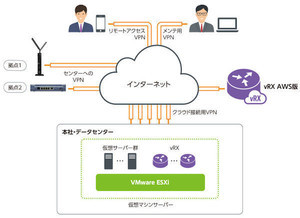

同技術を用いて、仮想ルーター「Tungsten Fabric」を、高速メモリHBM2を搭載した「Intel Stratix 10 MX FPGA」上に実装し、汎用サーバー上でのオフロード効果の検証を行ったという。

100Gbpsのイーサネットで接続したサーバー2台に仮想マシンを4台ずつ動かし、各仮想マシン間で通信を行って仮想ルーターの性能を測定したところ、パケット処理性能が約18倍に向上し、使用CPUコア数も従来の13コアから1コアに削減したという。

同技術により、低負荷・高性能な仮想ネットワークを提供し、5G時代の大量データを活用したビジネスにおいてサーバーの利用効率を向上させ、企業のDXを支えるとしている。