8月20日と21日に開催されたプロセッサに関する国際学会「Hot Chips 19」の最初のセッションにおいて、IBMは「POWER6」について3件の発表を行った。POWER6に関しては、昨年10月のFall Processor Forumにおいてアーキテクチャ中心の発表が行われ、今年2月のISSCCにおいてテクノロジ中心の発表が行われた。そして今回の発表は、エラー検出やエラーリカバリなどのRAS関係の詳細とキャッシュコヒーレンシ関係の発表だった。またもう一件の発表は、IBMがElastic Interfaceと呼ぶI/O回路に関するものだった。

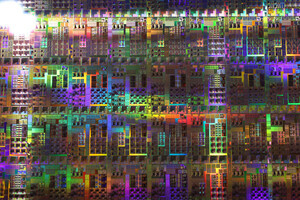

POWER6は、65nm CMOS SOIプロセスを使い、790M個のトランジスタを集積するデュアルコアプロセッサで、動作クロックは4.7GHzと驚異的に高い。そして、従来品と比較すると、それまではPowerPC系でしかサポートしていなかったVMX(ベクトルマルチメディアエクステンション)や10進浮動小数点演算などの機能を追加している。

各CPUコアは、64Kバイトの1次命令キャッシュと64Kバイトの1次データキャッシュ、そして4Mバイトの2次キャッシュを備えている。POWER5までは、2次キャッシュは2コアで共通であったが、POWER6ではクロックの高速化に伴い、2次キャッシュのアクセスレーテンシを抑えるために各コアに独立のキャッシュに変更された。そして別チップだが、32Mバイトの3次キャッシュを持つ構成であり、3次キャッシュのディレクトリとコントローラを内蔵している。