POWER6のRAS機能

POWER6はIBMのメインフレーム「z」シリーズのチームと共同開発を行い、メインフレームのRAS機能を取り入れたプロセッサとなった。単に、エラー頻度の高いキャッシュのSRAMアレイやシステムバスのエラーを検出および訂正するだけでなく、システムのどの部分でエラーが起きてもそれを検出し、リカバリが行えることを目指した設計になっている。

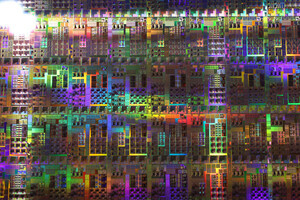

POWER6のエラー検出、リカバリの全体像を図1に示す。

まず、プロセッサコアはRecovery Unit(RU)というユニットを持ち、サイクルごとにコアのアーキテクチャ状態をこのユニット内のECCで保護されたRAMに格納する。そしてエラーが検出された場合は、プロセッサでの新しい命令の実行を停止し、RUに格納されたエラー発生以前の状態をコアのアーキテクチャレジスタに復元する。そして、復元した状態の直後の命令から実行を再開する。

そして、CPUのキャッシュや外部インタフェースはECCで100%保護されており、1ビットエラーを自動訂正する。また、そのほかのSRAMアレイやレジスタファイルも99%以上がパリティチェックで保護されており、前述の再実行でエラーを回復できる。さらにCPUののロジック部のエラーに関してもパリティーチェックやレジデューチェックで検出して再実行でエラーから回復を行う。

エラーが中性子などの一過性の故障によって引き起こされたものである場合は、この再実行でエラーを訂正することができる。また固定故障が起こり、再実行しても同じエラーとなる場合は、ハイパーバイザーに制御が移り、RUに格納されたエラー発生以前の状態をほかのコアにコピーして実行を再開するAlternate Processor Recovery機能をもっている。この状態の移動は同一チップ内のほかのコアに限らず、ほかのチップのコアにコピーすることも可能である。この機能により、固定故障の場合でも、予備のコアがあれば実行を継続することができる。

メモリDIMMに関しては、1ビットエラーはECCで訂正するが、コネクタの接触不良が起こると、これで1ビット訂正を使ってしまい、ほかの原因のエラーが起こると訂正不能な2ビットエラーになってしまう。このため、予備の入力ピンと出力ピンを備えたカスタムのDIMMを開発しており、これにより接続不良になったビットラインをこの予備ラインに切り替える。この機能を「Dynamic I/O Bitline repair」と呼んでいる。この機能により、次の定期保守まで1ビットエラー訂正可能な状態を維持して稼動を続け、定期保守時にDIMMを交換するなどの修理を行えば良い。

なお従来から採用されている機能だが、ChipKillはDIMM内の1個のDRAMが故障しても訂正可能なECC方式であり、DIMMに関しては2重、3重にエラー対策が施されている。

クロック発振器が止まることは滅多にないが、これが止まってしまうと前述のすべてのエラー対策はまったく役に立たず、システムダウンにつながる。そのため、2系統の発振器を備えており、一方の発振器が止まっても自動的に他方に切り替わり、CPU内部に供給されるクロックが途切れないDynamic Oscillator Failoverという機能を備えている。

なお、今回の発表では触れられなかったが、IBMのUNIXサーバである「p」シリーズなどでは電源や冷却ファンにも冗長設計が行われている。そのため、1個の電源やファンが故障してもシステムは止まらず、これらの故障したコンポーネントをシステムを稼動した状態で交換することができる。