TSMC Process - 20nmと16FF/16FF+の現状とその先

さてそのTSMC。28nmは既にMatureになり、引き続き多くの製品を量産している。この28nmの話はまた後でするとして、まずは20nmの現状から。NVIDIAは製品を放棄したが、用途さえ正しく選べば、ロジック密度の観点でメリットは十分にあるわけで、NVIDIAにしてもGM208は製品化に向けて進んでいる。

20nm世代の先陣を切ったのはFPGAで、Xilinxは2014年12月に20nmプロセスを利用したKintex Ultrascaleが量産体制に入ったことをアナウンスしている。20nm製品のTape Outは2013年7月だから16カ月ほど掛かった計算だが、これはEmbedded向け製品ということに加えて、初の20nmプロセスを使った製品ということで、念入りに動作検証を行ったためと思われる。

通常だとTape outから量産までの期間は(手直しがなければ)12カ月前後、GPUの様なコンシューマ向け製品であれば8~9カ月というあたりなので、今後はNetwork関連機器や一部Mobile関連機器を中心に20nmプロセスを利用した製品が増えてくるだろう。

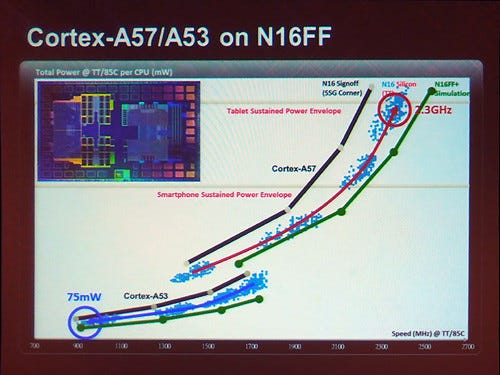

さて、メインとなるのは16nmのFinFETを使った16FF/16FF+であるが、これについてはちょっと面白い結果が出ている。Photo13はTSMCの16FFを使って、Cortex-A53とCortex-A57を試作した結果をまとめたものである。

黒の実線はSign Off、つまり設計終了の段階で想定した動作周波数と消費電力の関係をプロットしたもので、水色の点は実際に試作したシリコンでの実績、赤はこれをまとめたものだ。

この場合、グラフが右下に移動するほど特性が良好ということであり、例えばCortex-53の場合は900MHzにおける消費電力が90mW程度を予定していたのが80mW是前後になり、また1.7GHzにおける消費電力も若干低めに収まっている。Cortex-A57のほうはもっと顕著で、特に2GHz付近の動作周波数では消費電力が1W近く違うし、最大動作周波数も100MHzほどアップしている。

そんなわけで16FFは実際のシリコンは優秀な結果を収めているという話であるが、この16FFに続いて用意しているのが16FF+で、これは16FFの改良版という扱いである。Photo13に緑色で示されているのが、16FF+のシミュレーションの結果である。こちらはまだSign Off時点の値ではないから同列に比較するのは難しいが、それでも実際の16FFシリコンよりも省電力ないし高動作周波数が見込めるとしている。

NVIDIA GPUの所でも紹介した通り、すでにHiSiliconのD01という動作サンプル(ただしES以前のαサンプルの段階)も存在しており、少なくともこの16FF(やその後継の16FF+)について、技術的な観点での不安はあまり無い状況といってよい。

気がかりなのは製造能力の方である。現在TSMCは12inchのGIGAFABを3つ(GIGAFAB 12/14/15)保有しており、GIGAFAB 12と14はPhase 1~7、GIGAFAB15はPhase 1~4の設備を保有している(ちなみにうち3つは現在立ち上がり中で、1つは建設中)が、この大半は28nmプロセスなどの製造に利用されており、20nmと16FF/16FF+についてはいまのところFab 14に限られている。2014年第3四半期には16FFの量産を開始しており、これは主にGIGAFAB 14のPhase 5の一部とPhase 6が担っている。

2015年にはPhase 6もフル稼働し、さらに建設中のPhase 7も立ち上げに入っていると思うが、明らかにデマンドに対する生産能力は足りないと思われる。後述の理由で28nmの生産量を短期的に減らす予定も無さそうであり、今後16FF/16FF+の需要増加をどう賄うつもりなのかはちょっと謎が残るところだ。

もっと不明瞭なのが10nmプロセスである。TSMCはここで完全にIntelをCacheupしたいともくろんでおり、2016年にはRisk Productionを開始させたいとしてしている。もっともこれが本当に可能かどうか、というのは微妙なところ。Intelによる見解は前述した通りだが、複数の業界関係者に尋ねたところ、一様に10nmは難しいだろうと見ており、2016年のRisk Productionはちょっと疑問である。

あともう1つネックになるのが露光の問題だ。16nmでもArF+液浸ではダブルパターニングが当たり前で、これがNREコストの高騰(マスク数が半端無い)とウェハコストの高騰(マルチパターニングが増えるほど処理コストが増えるから)を招く大きな要因だが、だからといってEUVは相変わらずの状況である。EUVに関するGlobalFoundriesの見解はこちらでもちょっと触れたが、Double/Triple Patterningでは現状のEUVの光源出力(連続で40W程度)だと話にならない。

ところが半導体製造装置メーカーであるASMLの幹部によれば、例えば10nmなら18mask、7nm世代に至っては27maskが必要になり、そうなるとArF+液浸でのスループットは現在の1/6~1/10に落ちる計算になる。現状はTriple Patterningで100Wafer/時強~200Wafer/時弱というのが一般的な処理速度であるが、10nm世代だとこれが20Wafer/Hour前後まで落ちてしまう計算だ。

つまり200Wafer/日程度という計算だが、すでに現状のEUVでは100Wafer/日を実現しているから、EUV露光装置2台あればつじつまがあう計算になる。むしろこの場合マスクコストが大幅に減るから、NREの低減というおまけも付く。

ただこれはある意味むちゃな議論であって、実際に200Wafer/日で生産していたら、さまざまな顧客の需要に応えることはできない。ちなみにASMLのEUV Stepperの金額は非公開だが、量産機(NXE:3300 最近はこの改良型のNXE:3300BとかNXE:3350Bが存在する)の前に同社が出荷したNXE:3100という試作機は1台6000万EUROであった。そう考えると、EUVを導入した場合はこの償却コストがばかにならないため、200Wafer/day程度の生産量では全然割に合わない。このあたりも10nm世代ではまだ見通しがはっきりしないままとなっている。

TMSCの最後に28nmの話を。当初LP(Low Power)/HPL(High Performance Low Power)/HP(High Performance)の3つのプロセスオプションでスタートしたが、その後モバイル向けのHPM(High Performance Mobile)を追加、さらにHPMを低価格化したといっても良いHPC(High Performance Compact mobile computing)を追加している。

HPMとHPCの違いは、HPMがCortex-A15とかCortex-A57の様な、2GHzを超える動作周波数も可能なMobile向けなのに対し、HPCはCortex-A7とかCortex-A53といった、1.5GHzあたりを上限とするMobile向けというところで、HPMと比較して10%ダイサイズを減らしつつ、30%消費電力を下げることが可能になっている。

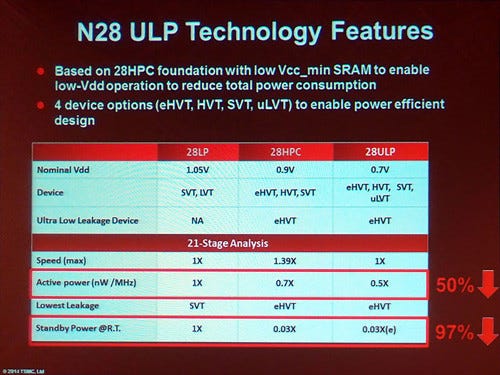

このシリーズの最新のものが、10月に発表された28ULP(Ultra Low Power)で、28LPと比較して大幅に消費電力を下げられるプロセスとなっている(Photo14)。この28ULPのターゲットはWearable DeviceやIoTデバイスなどとにかく長時間の待機時間が求められる用途向けで、これまではもっと古いプロセスを利用して製造されていたこうしたデバイスを28nmプロセスに取り込もう、というもくろみである。

こうしたバリエーションの追加により、向こう10年間は28nmプロセスがさまざまな用途で使われるだろうというのが同社の見解なので、当面28nmプロセスの製造Fabがあくことは無いだろうと見られる。