Intel Process - 14nmにおける苦戦の要因とは

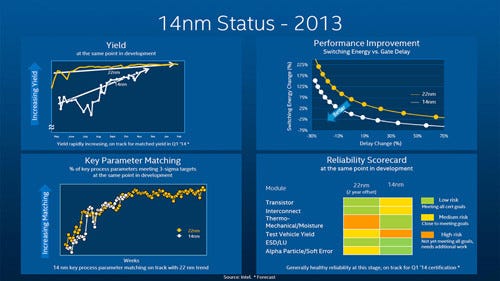

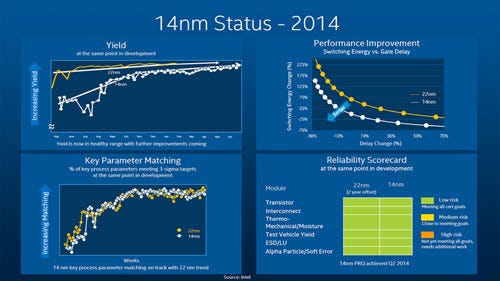

最後にプロセスの話を少し。まずは苦闘しているIntelの14nmプロセスの話について。Photo08~Photo12は2014年11月に開催されたIntelのInvestor Meetingで示されたプレゼンテーションである。Photo08は2013年のInvestor Meetingで示されたもので、Photo09は2014年度版に更新したものである。

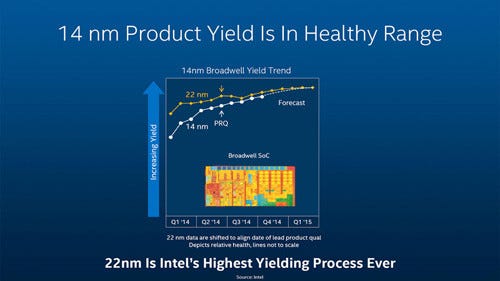

これだけ見ていれば、非常に順調に進展しているように見えなくも無い。Yield(歩留まり)も順調に改善しており、主要な製造パラメータも22nmと同等レベルまで改善され、信頼性に関しても全ての項目でLow Riskになっている。

ものがInvestor Meetingだけに、ここでの情報そのものは信頼できる(でなければ投資家に嘘をつくことになるから、万一バレたりしたらManagement Teamと取締役会メンバーが全員逮捕されかねない)と考えてよい。また製品としてのYieldも次第に改善していることが示されている(Photo10)。では何でBroadwellの出荷が進まず、それどころかRespinを重ねているのかということだ。

|

Photo10:Q2'14の"PRQ"は"Production Release Qualification"の意味で、出荷できる品質に達したの意味。それが事実ならもう市場にBroadwell搭載製品が溢れていてもおかしくないのだが…… |

実はこれに関してはIntelの中でもトップシークレットに近い話らしく、少なくとも現状では一切正式な話はわからない。ただ、いくつかの情報をあわせた上で判断すると、限界性能のぶれが収まらないという話で、その部分のコントロールに相当難儀しているらしい。

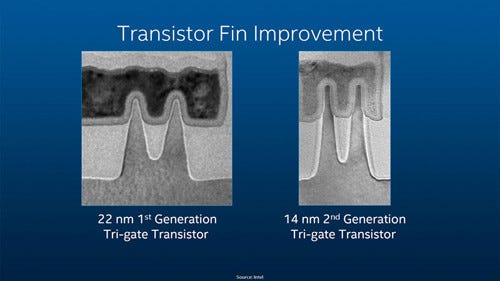

ちょっと話が飛ぶが、2年ほど前に日立中研の久本大氏にFinFETのお話を伺った時に、「Finを作ってみた時に、Finの幅を10nm以下にして行くと、Vtのしきい値が量子効果でずれるんですよね」という話があった。

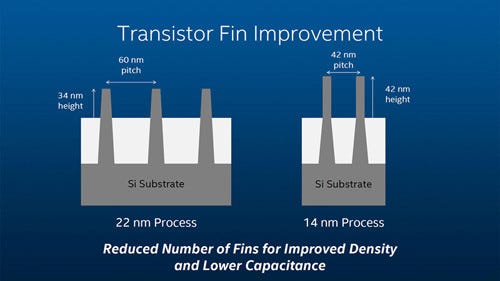

どうもIntelが直面している問題は、まさしくこういう話に近いらしい。Intelは14nmのFinFETプロセスの概略(Photo11)やTEM写真(Photo12)を公開しているが、ここまでFinの厚みが薄いとそろそろ量子効果の影響を考えないといけないレベルになっているように思える。

久本氏の話はあくまでR&Dのレベルの話だから10nmぎりぎりまでいける(10nmあたりに敷居がある)という話だったが、実際に量産ラインでは14nmあたりで限界に近づいているのではないかということらしい。

この結果として、何度かトランジスタの形状の変更を含む変更が行われ、そうなると当然Respinが発生するということのようだ。ただ、一応Intelとしてはこの問題に解決の目処が立ったようで、H Steppingではまともに製品が出せると予定しているらしい。

もっともこれが単に形状の変更だけで済むのか、あるいは材料を含む変更なのか、もしくは回路レベルでの何かしらの解決策(Body Biasまでは投入しないと思うが)があったのかは不明であり、関係者によれば「そうした内容は、少なくとも1年以上たたない限り公開されないだろう」としている。ただ、同じ関係者によれば、これを14nm世代で解決することで、10nmでは問題なくそのまま行けるだろうと見ているようだ。

実はこの話はTSMCやGlobalFoundriesにも関係してくる。TSMCの16FFとか16FF+といったプロセスは、構造的にはIntelの22nm FinFETに近いものなので、スムーズに行くが、TSMCが次に予定している10nm世代ではIntelの14nmと同じ問題に直面することになり、解決に苦労するだろうとIntel社内では判断しているそうだ。

Intelとしてはむやみに敵に塩を送る理由はなく、特にこれからFoundary Businessに乗り出す以上、無駄にTSMCに利する情報を公開する理由がないので、Intelがこの14nmに関する問題の詳細を発表するのは、当分先になるのではないかと思われる。