|

|

論文を発表するNVIDIAのOreste Villa氏 |

SC14においてNVIDIAは、「Scaling the Power Wall:A Path to Exascale」と題する論文を発表した。

NVIDIAは2010年から開始されたDARPAのExtreme-Scale Computing Projectの開発を受託しており、その一環としての研究成果の発表と思われる。

Oak Ridge国立研究所のTitanスパコンは18,688台のTesla K20x GPUを使って9MWのピーク電力を消費して、17.59PFlopsのLINPACK性能を実現している。これは、おおよそ2GFlops/Wのエネルギー効率である。

DARPAプロジェクトのターゲットは2022年であるが、これはシステムの完成時期であるので、その2年前の2020年のテクノロジを考えると、現在の28nmプロセスが7nmにシュリンクできると予想され、テクノロジ的には4倍の性能改善ができると見込まれる。これに加えて、回路設計とアーキテクチャで6倍の改善を実現できれば、Titanの25倍の50GFlops/Wを実現できる計算になる。こうなれば、50倍の性能である1000PFlopsを、2倍の20MWの消費電力で実現できることになる。

|

|

|

現在のTitanスパコンはLINPACK 17.59PFlopsを9MWで実現している。これはおおよそ2GFlops/W |

2020年の7nmテクノロジの使用で4倍の改善。回路とアーキテクチャで6倍改善すれば、1000PFlopsを20MWで実現できる |

エネルギー省が代表的と考えているアプリケーションは、有限要素法のMiniFE、中性子移送問題を解くSNAPやXSBenchなど6種のプログラムで、これらのアプリケーションを実行するときのエネルギー効率を25倍改善できるかが課題である。

これに対して、NVIDIAは右側の図のようなアーキテクチャの計算ノードを提案している。スループットに最適化した多数のTOCコア(Throughput Optimized Core)とレーテンシに最適化した比較的少数のLOCコア(Latency Optimized Core)を集積し、これらとメモリコントローラ、ネットワークインタフェースコントローラ群をチップ上のネットワークで結合する。なお、この構造はSC10でNVIDIAが発表したものと同じである。

|

|

|

DoEが代表として選んだ6種のアプリケーション。これらで50倍の性能向上を2倍の電力で実現するのが目標 |

NVIDIAが提案している計算ノードの構成。スループットに最適化したTOCとレーテンシに最適化したLOCを集積するヘテロなチップ |

ノード構成の詳細は次の左側の図に書かれているが、TOCは512個、LOCは8個、TOCが持つ倍精度(Double Precision)浮動小数点演算器は16個、メモリコントローラは8個、NICは100GB/sのものを4個集積する。

7nmプロセスを使って、チップサイズは650mm2、クロックは1GHz、電源電圧は0.65Vで消費電力は230Wと見積もられている。メモリにはHBM(High Bandwidth Memory)を使いこのノードのメモリバンド幅は4TB/s、DP演算性能は16TFlopsとなる。そして、キャビネットに384ノードを収容し、このキャビネットを200個並べると1.3ExaFlopsを23MWで実現できる。

6倍の回路設計、アーキテクチャの改善であるが、その第一の改善候補はワープ幅の短縮である。現在のNVIDIAのGPUでは32個のスレッドをまとめて同じ命令を実行している。これをNVIDIAは「Warp」と呼んでいる。

しかし、条件分岐命令がWarpに含まれる場合は、分岐するスレッドでは分岐で飛び越される命令を空実行することになり、ムダなエネルギーを消費する。このように実行の流れが分かれてしまうことを「Divergence」と呼ぶ。右の図の棒グラフのように、Divergenceが起こった時にどれだけのスレッドが有効に実行されるかはアプリケーションとWarpサイズに依存する。NVIDIAの研究では、現状のWarpサイズが32の場合は41%の命令しか有効に利用できないが、Warpサイズを4に短縮すると65%有効に利用できるようになるという。

|

|

|

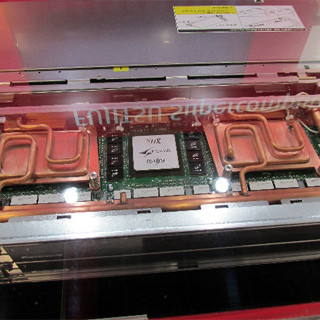

ノードは512個のTOCと8個のLOCを集積し、消費電力230W。384ノードをキャビネットに入れ、200キャビネットで1.3ExaFlopsのシステムを構成する |

条件分岐の方向の異なるスレッドがワープ内に混在すると空実行が入り、効率が低下する。ワープのサイズを小さくすると、空実行が減り、効率が向上する |

Warpの各スレッドはすべて同じ命令を実行するが、そのオペランドがスレッドごとに異なる場合はそれぞれの命令の実行は意味があるが、まったく同じオペランドを使い、同じ計算をする場合もある。後者の場合は1カ所で演算すれば良く、その他のスレッドでのレジスタファイルの読み書きや演算のエネルギーはムダに使われている。第2の改善候補は、このようなムダなケースをコンパイラで検出して、1つの演算ユニットだけで計算するようにすることでエネルギー消費のムダを省く。