この新世代アイサイトは、2眼レンズを使ったステレオカメラによって、前方の衝突物との距離を単眼カメラよりも正確に測定し、すぐに停止できるようになっている。

Xilinxは、2015年6月に新型Zynq Ultrascale+ MPSoCを使ったADASシステムを提案していたが、この時のプログラマブルSoCと今回のMPSoCは同じではない。もちろん進化している。5年前は28nmプロセスを採用したSoCであったが、今回採用されたMPSoCは16nmプロセスへ微細化されたものである。今回、ステレオビジョンを使った自動ブレーキシステムでは視野角が広がったことで、事故をさらに減らすことが可能になっている。

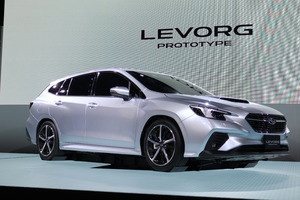

新型レヴォーグでは、搭載されたステレオカメラで前方の視野角を広げることによって、事故の大部分を占める交差点での事故を減らすことができる可能性が高まったようだ。歩行者の巻き込みや右折車と直進車との衝突、出会い頭の衝突などを避けることができるようになるためだ (図2)。加えて、ドライバーの意識喪失やわき見運転の警告を発するモニタリングシステムなどもすでに搭載されている。

さらに、今回は、レーンキーピング支援(LKA)機能やアダプティブクルーズコントロール(ACC)も搭載している(図3)。LKAにより、隣接車線の有無を検出し、カーブに差し掛かるときを予測し自動的に減速する機能も可能になる。ACC機能を使えば、渋滞時にハンズオフで自動的に運転してくれる。

このSoCは、ADASの高度化と共に進化されてきた。その背景には半導体のプロセスの微細化があり、これによりデータ処理能力が向上し、高速応答が可能になった。かつて衝突防止の技術として、前方を検出するセンサには、カメラ方式かレーダー方式か、という議論があったが、高価だったレーダー方式は安価になり、カメラ方式とレーダー方式の両方を使うケースも出てきている。SUBARUの新型レヴォーグでは、前方はステレオカメラで視野角を広げ、周囲は四隅のレーダーで検出する方式をとっている。

クルマ用途におけるFPGAという存在は、5年ほど前は試作車向けにさまざまなことを試してみる半導体として使われることが多かった。クルマのADAS向けの仕様が決まればすぐに試せるというメリットがあったからだ。ところが近年、ADASの仕様や機能は毎年、更新・強化され、もはやASICのような専用チップでは時間的に対応できないことがはっきりしてきた。専用チップの設計・製造には2~4年ほどの時間がかかるからだ。加えて、専用ASICで採用するプロセスよりもFPGAの方が微細なプロセスを使っていることも多く、性能的にも有利となっており、プログラマブルの半導体が適していることが明確になってきた。

また、前方のカメラ映像だけではなく、周辺のクルマを検出するレーダーからのデータも取り込み、処理するセンサフュージョン機能をFPGAで実現することも増えてきたという。センサフュージョンは、どのようなセンサを用いるかによってどのようなデータを処理すべきかが決まるため、究極の少量多品種製品となる。このためASICを設計・製造するのではなくFPGAの方が調達が適している。

ただ、プログラマブルと言っても、CPUのようにソフトウェアでプログラムを処理する場合と、FPGAのように専用ハードウェアで回路を組む場合に分かれる点に注意が必要となる。ソフトウェアによる処理ならプログラムを組む時間さえあれば、デバッグやコンパイラする時間はあるものの、ハードウェアに落とし込むための作業は要らないため早期に出来上がる。このため制御や簡単な演算プログラムはCPUで演算処理し、複雑な演算が必要な場合にはGPUで処理することで高速でフレキシブルな機能が可能になる。そして、より高速化したい場合は、FPGAで専用の高速処理回路を作ってしまえばよい。電子システムは、CPUやGPUとFPGAの3つがあればかなりの機能を実現できるようになった。最近ではAI専用回路(MAC演算+メモリ)を加える場合も増えている。

-

図4 Zynq Ultrascale+ MPSoCのブロックダイヤグラム。演算を強化する場合は上段のArm Cortex-A53およびGPUコアのMali-400MPなどを使い、低消費電力で動作させる場合はCortex-R5コアで対応する (資料提供:Xilinx)

この点、Zynq Ultrascale+ MPSoC自体が進化すると共に、かなりの演算機能に対応できるようになっていく(図4)。MPSoCでは、演算を強化する時はハイパフォーマンスのArm Cortex-A53のクワッドコアと演算用GPUのMali-400を使い、消費電力を抑えいときはArm Cortex-R5デュアルコアを利用する。また、特殊な入出力インタフェースやハードウェアのAIエンジンを活用する場合にはFPGAのロジックセル部分を使う。

Xilinxは、これからのクルマに必要な機能として、これまでのレーダーやLiDAR、ステレオカメラなどに加えて、ドメインコントローラの必要性も提案している(図5)。ドメインコントローラはECUが増えすぎて車両が重くなることを防ぐことを目的に、複数のECUをまとめる回路モジュールだが、外部からの通信を経て最初のコンピュータとなるゲートウェイ機能も持たせるものもある。ゲートウェイから各ECUあるいは別のドメインコントローラへ情報を送り、送られた先のドメインコントローラでエッジコンピューティング機能やデータ収集・処理・配信機能を担う。

AI(機械学習やディープラーニングの推論)で処理する部分が増えてくれば、よりハイエンドなプログラマブル半導体「Versal ACAP(Adaptive Compute Acceleration Platform)」を使うことも可能になる。Xilinxのソリューションは、さまざまなプラットフォームに対応しており、ソフトウェアとハードウェアのプログラムが可能な半導体として利用できる。クルマのADASシステムの進化が続く限り、ASICやASSPなどはもはやソリューションにはなりにくくなっている。

参考資料