この論文で提案する「Line Recycling(LR)」の考え方を次の図に示す。次の図のように不良ビットを持つ3つのキャッシュラインを考える。この3つのキャッシュラインは同じビット位置に不良ビットが重ならないように選ぶ。

この例でset0 way3のエラーを訂正してそのキャッシュラインをリサイクルする場合、同じビット位置にエラーの無い2つのキャッシュラインをパッチラインとする。そして、set0 way3に書き込む場合は同じデータをパッチラインにも書き込む。パッチラインの赤で示したビットにエラーがあっても、リサイクルするset0 way3のエラービットと位置が重なってなければ良いので、2セットをパッチラインに使えばいくつものエラーの訂正に使える。

そしてset0 way3を読み出す場合は2つのパッチラインも読み出して多数決を取ると正しい値を得ることができる。

1つのエラーを訂正するのに2つのラインをパッチラインとして使うので、その分、キャッシュの容量が減るが、パッチラインにエラーが無いことは要求されないので、パッチラインの候補は容易に見つかりオーバヘッドとしては大きくないと思われる。

また、このLR法では、エラーを訂正してリサイクルするためには、2つのパッチラインにも同じデータを書き込む必要があり、読み出しの場合には2つのパッチラインも読み出す必要があり、Read/Writeともに3回のキャッシュアクセスが必要となる。このため、キャッシュのアクセス時間が長くなり、電力が増えるというデメリットがある。

さらに、TLBにパッチラインのアドレスを書いて置く必要があるなど、いろいろなオーバヘッドがある。

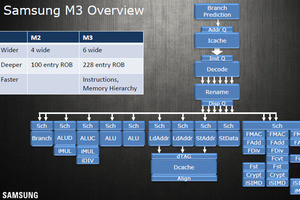

BOOMの開発環境であるが、次の図に示すようにBOOMv1とBOOMv2ではパイプラインダイヤグラムも変わり大きな設計変更が行われているが、僅か4か月でこの設計変更を行っているように非常にアジャイルな開発環境が構築されている。

次の図に完成したBOOMチップの諸元とチップ写真、ブロックダイヤを示す。命令フェッチは2命令並列で、命令を分解したマイクロ命令のレベルでは最大4命令を同時に発行できる。L1キャッシュは命令、データともに4wayで16KB。L2キャッシュは8wayで1MBである。チップ写真に見られるように、L2キャッシュが全体の6割程度の面積を占めている。

次の図に実験のセットアップを示す。手前のボードに前述のBOOMチップが搭載されている。奥のボードはXilinxのZC706を搭載したボードで、Xilinxのチップの中に入っているCortex-A9プロセサがBOOMを使うコンピュータのフロントエンドサーバとして動いている。

BOOMチップは0.9Vの電源で1GHzのクロックで動作し、Coremark/MHzは3.77でIPCは1.11を計測した。なお、このチップは0.6V電源でも320MHzクロックで動作した。

次の図の左側のグラフは、電源電圧(この図の横軸は[V]ではなく任意単位[a.u.])とビットエラー率の関係を示したもので、例えばL2キャッシュの場合は、Vddが0.6の場合は

10-7のエラー率であるが、Vddが0.45まで下がるとエラー率は3×10-4と300倍になる。

右側の棒グラフは何の対策も取らない場合は、電源電圧は0.6[a.u.]必要であり、これを下回ると正常に動作しなくなる。しかし、各種の低電圧での動作不良ビットを切り離したり、マスクしたりすると、より低い電源電圧でも動作させられる。

この論文で提案するLine Recycling(LR)という方法で5%のキャッシュ容量のロスを許容すると、動作電圧を21.7%下げることができ、消費電力を43%低減することができた。

次の図はL2キャッシュのSRAMのシュムープロットであるが、対角線の下の右側の緑の部分は、特別な対策を行わなくても正常に動作する領域、対角線の上の赤の部分は動作しない領域である。そして黄色の部分が、LRで不良ビットに対策を施したらSRAMが正常に動作する部分である。LRの対策なしでは電源電圧0.6程度が下限であるが、LRで対策を行えば、 0.47まで動作域が広がる。ただし、0.47の電源では、動作周波数は70MHzと低くなる。

なお、この図では下限は0.47Vと書かれており、任意単位[a.u.]は[V]と同じであるようである。

BOOMコアは、アジャイルな設計メソドロジの研究、ハードウェアとソフトウェアのコデザインの研究、SpectreやMeltdownのような攻撃をどう防ぐかなどのセキュリティの研究、新たなRISC-Vアーキテクチャの研究など、いろいろな用途に使うことができる。