カリフォルニア大学バークレイ校(UCB)が開発したRISC-V(リスクファイブ)アーキテクチャはライセンスフリーのプロセサアーキテクチャとしてディスク大手のWestern DigitalやGPU大手のNVIDIAがコントローラとして全面的な採用を決めるなど支持が広がっている。

UCBは命令アーキテクチャだけでなくRISC-Vコアも開発しており、Rocketコアというインオーダのコアを公開している。Arm-M0のような低レベルのコントローラとしてはRocketコアで良いが、より高性能なプロセサコアが欲しいという要求もあり、2010年ころから、「Berkeley Out-of-Order Machine(BOOM)」の研究が行われてきた。その結晶として2017年にはBROOMチップがテープアウトされ、今回のHot Chipsで発表されるという流れになっている。

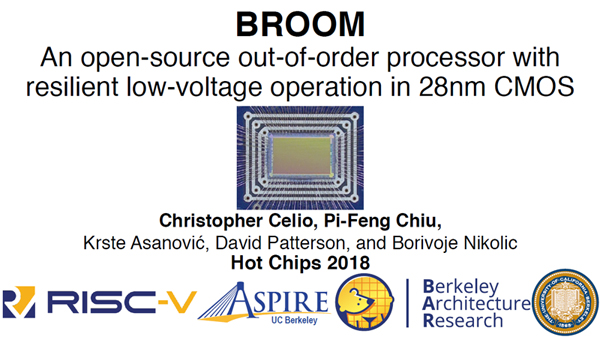

次の図は発表のタイトルスライドであるが、Christopher Celio氏とPi-Feng Chiu氏がHot Chips 30での発表者であるが、その他にRISC-Vの創始者のKrste Asanović教授、同じくRISC-V創始者で、RISCの名付け親、ヘネパタ本などで有名なDavid Patterson教授、プロセサの回路寄りの研究で有名なBorivoje Nikolic教授とオールスターが名を連ねている。

-

RISC-VのBROOMコアの発表のタイトルスライド (出典:この連載のすべての図は、Hot Chips 30でのIntelのChristopher Celio氏とPi-Feng Chiu氏の発表スライドのコピーである)

発表のタイトルではBROOMであるが、プロセサのマイクロアーキテクチャはBOOM(Berkeley Out-of-Order Machine)となっており、発表を聞いたが、BOOMとBROOMの使い分けはよくわからなかった。

BOOMはRISC-VのRV64G命令セットを実装したスーパスカラのOut-of-Order実行マシンであり、現在公開されているIn-OrderのRocketコアより高性能のコアである。ただし、プロセサコア以外の周辺などはRocketチップのものを利用している。

また、設計言語としてはChiselを使っており、BOOMはオープンソースの合成可能なプロセサコアである。

次の図の上に書かれているのはBROOMコアのパイプラインダイヤグラムで、右下に描かれているのはBROOMコアのダイプロットである。自動配置配線CADを使っているので、各ユニットの境界は直線ではなく、国境を示す地図のようになっている。

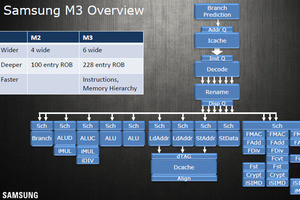

次の図は、前出のパイプラインダイヤグラムをもう少し詳しく書いたものである。命令フェッチが3段、デコードとリネームしてディスパッチするのに計2段、レジスタからのオペランドの読み出しに1段のパイプラインとなっている。

実行パイプラインは、ロード、ストア各1本、ALUだけのパイプラインとALU/iDiv/iMulのパイプラインと整数から浮動小数点への変換パイプラインを備えている。そして、浮動小数点演算は、整数への型変換/除算/積和計算のFMA演算器をもつパイプラインを備えている。

RISC-Vとしては、Rocketコアより高性能のコアであるが、スーパスカラのOut-of-Orderマシンとしては最小限の簡素なマシンという感じで、サーバ用のCPUには及ばない。

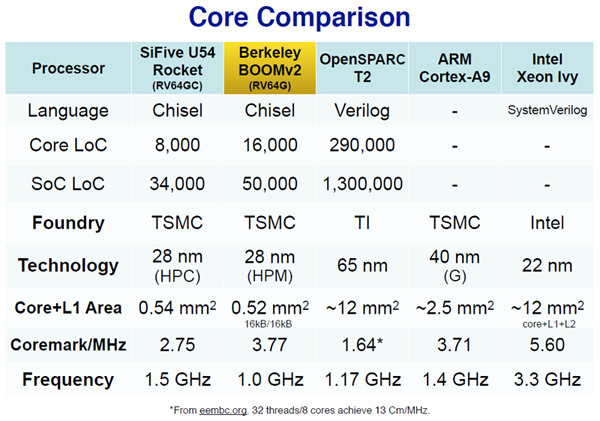

次の表は、RISC-VのRocketコアとBOOMv2コア、そしてOpenSPARC T2、Arm Cortex-A9、Intel Xeon(Ivy Bridgeコア)の諸元を比較したものである。BOOMは16,000行のChiselで書かれており、Rocketの2倍であるが、かなりコンパクトである。プロセスが28nmと40nmという違いがあるが、BOOMはCortex-A9と比較して面積が小さく、Coremark/MHzも同程度で、十分、競争できるコアであると思われる。

プロセサコアとしては性能/Wが最も重要な指標である。消費電力を減らす最も有効な方法は電源電圧を下げることであるが、電源を下げると、まず、動作しなくなるのがキャッシュなどに使うSRAMである。このため、BOOMのプロジェクトではキャッシュのSRAMの電源電圧を下げて動作させる手法について研究を行った。

ビット密度を高めるため、SRAMには微小なトランジスタが使われるが、微小であるので小さな製造バラつきでもトランジスタの特性の変動が大きく、低電圧になるにつれて正常に動作しないメモリセルが増加する。

エラー対策というと、ECCなどで誤ったビットを訂正することを思い浮かべるが、この論文でのエラー対策は、動作しないビットセルがあるキャッシュラインを無効化したり、スペアの動作する部分と交換するなどの方法で、キャッシュとして正常に動作するようにすることを指している。

この方法は半導体プロセスに依存する回路の変更などを必要とせず、RTLの変更だけで動作不良のビットを排除することができ、半導体プロセスが変わっても適用できる。

-

対角線より上の赤の領域は、動作しない領域。対角線の下でVminより高い電源電圧の緑の領域が動作領域。黄色の領域はキャッシュSRAMはエラーするが、エラーするビットを排除して使えばより低い電源電圧まで動作させられる領域である

(次回は10月2日に掲載します)