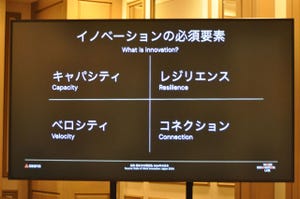

東京ビッグサイトにて12月13日~15日にかけて開催されているエレクトロニクス製造サプライチェーンの国際展示会「SEMICON Japan 2023」にて、シーメンスEDAジャパンは、2.5D/3Dチップレットの開発を容易化するソリューション群の紹介を行っている。

シーメンスEDAは、元々EDAベンダ大手のMentor Graphicsを前身としており、Mentorが2017年にシーメンスに買収された後、2021年1月の法的統合の完了により現在の社名へと変更されたもの。Mentor時代から引き続き、さまざまなEDAツールを提供してきており、その製品ラインナップも半導体デバイス設計からパッケージ、プリント基板まで幅広いことが特徴となっている。

今回の同社ブースでも半導体設計とプリント基板設計の両側面を1社として手掛けてきたことを強みに、半導体デバイス設計からチップレットまで一気通貫で取り組むことが可能となる点を強調したソリューションの紹介を行っている。

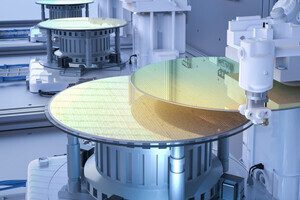

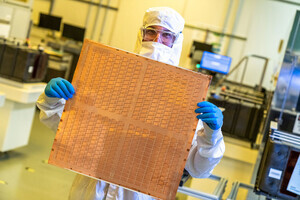

具体的には、同社の物理検証ツール「Calibre」で用いられているダイレベルのサインオフ検証を拡張し、2.5D/3Dなど幅広いスタック・ダイ設計のサインオフ検証を可能とする「Calibre 3DSTACK」、2.5D/3D ICパッケージンのプランニングとプロトタイピングを行える「Xpedition Substrate Integrator」、ICパッケージのインタフェース設計や接続検証などを行える「Xpedition IC Packaging Solutions」、2.5D/3D IC設計における複雑なDFT(Design for Testability)タスクに対応することを目的に開発されたDFT自動化ソリューション「Tessent Multi-die」などが紹介されている。

チップレットは、複数のチップを組み合わせて1チップを構成するため、組み立てがシングルダイのチップに比べて複雑化することが課題となる。この点について同社では、IC設計側、プリント基板/パッケージ側の両方を同時に見てきたノウハウを強みとするほか、そうした背景を持つ稀有な存在として、チップレットの普及促進に向けて、それぞれのユーザーをつないでいく役割を担っていきたいとしており、そのほかのさまざまな解析ツールなども含め、より高性能化が求められる半導体設計に向け、ユーザーが使いやすい高性能なツールソリューションを提供していきたいとしていた。