東京大学(東大)は12月5日、スピン系の時間発展のシミュレーションを通じて、量子コンピュータの「超伝導型」と「イオントラップ型」の2種類の方式のパフォーマンスを比較し、それぞれの特性を明らかにしたことを発表した。

同成果は、東大大学院 理学系研究科のエリック・ローツステット准教授、東大 アト秒レーザー科学研究機構の山内薫特任教授らの共同研究チームによるもの。詳細は、化学物理に関する全般を扱う学術誌「Chemical Physics Letters」に掲載された。

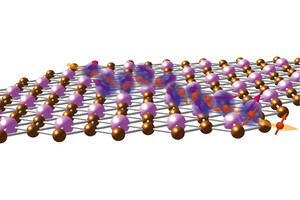

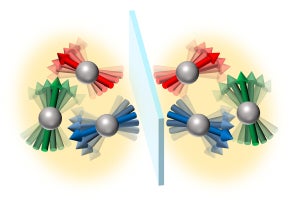

量子コンピュータの根幹となる量子ビットを実現するための方式には、さまざまな種類がある。その中で、量子ビットがミリケルビン温度まで冷却された超伝導回路として実現される超伝導型と、高周波電場によってトラップされたイッテルビウムやカルシウムなどの原子イオンを用いて実現されるイオントラップ型については、現在ユーザーのためのプラットフォームが用意されており、それらの性能や特長を活かした量子アルゴリズムの開発も進められている。ところが、両方式の性能がどのように異なるのか、具体的なシミュレーションを基に比較した例は知られておらず、両方式の量子コンピュータを用いて共通の問題を解き、そのパフォーマンスを比較することが待ち望まれていたとする。

そこで今回の研究では、超伝導型としてIBMの最新モデル「ibm_prague」(Heronプロセッサのプロトタイプを搭載)を、イオントラップ型としてQuantinuumの最新モデルの1つである「H1-1」を用いて、最も基本的な1次元3サイトHeisenbergスピン系のダイナミクスの計算を行い、その結果を比較することで、これからの量子コンピュータを活用した基礎・応用研究への指針を与えることを試みたという。

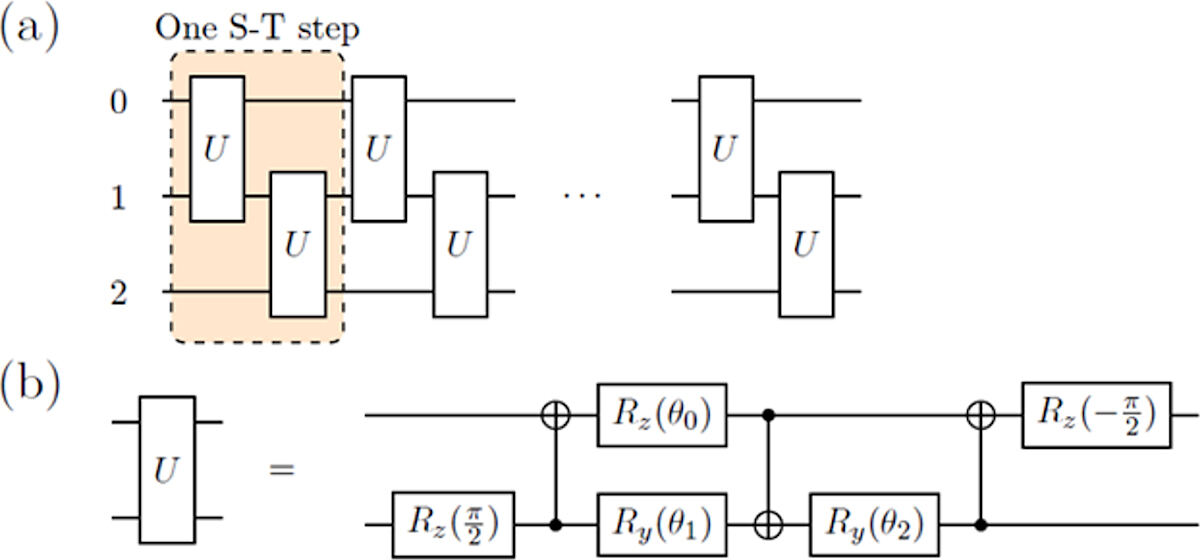

今回のシミュレーションでは、3つの量子ビットを使用し、演算子の和を指数部に持つ演算子を各々の演算子の指数演算子の積に分解する「Suzuki-Trotter近似」を使用して、時間依存ダイナミクスの量子計算が行われた。

研究チームによれば、今回の2機も含め現在一般に利用可能な量子コンピュータは中規模の「NISQデバイス」であるといい、環境との相互作用から生じる多くの種類のノイズのために量子演算にエラーが生じてしまう。そのため、量子コンピュータで実行された計算結果から意味のある結果を抽出するためには、ノイズの影響を減らす「誤り抑制」を行うことが必要である。

ibm_pragueの場合には、「ダイナミック・デカップリング」、「パウリ・トワーリング」、「読み出しエラーの抑制」という3つのエラー抑制を行った上で、スピンを保存しない状態を除去して波動関数を正規化した結果が得られ、古典コンピュータで得られた正しい結果をほぼ完全に再現したという。

また一方のH1-1の場合には、得られた結果そのままで古典コンピュータによって得られた正しい結果をほぼ再現しており、スピンを保存しない状態を除去して波動関数を正規化しただけで結果が得られ、正しい結果をほぼ完全に再現することが確認された。

-

量子ビット状態|110>の分布の時間発展。(a)イオントラップ型のH1-1による結果。(b)超伝導型のibm_pragueによる結果。ダイナミック・デカップリング(DD)、パウリ・トワーリング(PT)、読み出しエラーの抑制(M3)の3種のエラー抑制手法が用いられている(出所:東大Webサイト)

なおH1-1の場合は、データ点ごとに1024回の測定を行っており、各測定には約225ミリ秒を要したのに対し、ibm_pragueの場合にはデータ点ごとに5万48回の測定が行われ、各測定に約1ミリ秒かかったする。このことから各測定にかかる時間について、H1-1はibm_pragueに比べて約200倍の時間がかかることがわかった。また、データ点1つごとにかかった時間は、H1-1の場合には230秒だったのに対して、ibm_pragueの場合には50秒だったとしている。

今回の研究において、超伝導型およびイオントラップ型のそれぞれのハイエンドマシンを用いて、量子スピンダイナミクスのシミュレーションが行われた結果、両方式の量子コンピュータともに量子ダイナミクスを正確にシミュレーションできるレベルにあることが示された。さらに、超伝導型を用いた場合はエラー抑制が必要となるが計算速度が速いという特徴を持つこと、イオントラップ型を用いた場合は計算速度が遅いものの計算の精度が非常に高いという特徴を持つことが明らかにされた。

将来、量子コンピュータのハードウエア開発が進展しすることで、NISQデバイスの性能が高くなり、より大きくて複雑なシステムを計算するために量子コンピュータが活用されていくものと予想される。今回の研究成果はそのような場合において、それぞれのNISQデバイスの性能やパフォーマンスに応じて、最適なエラー抑制の方法を開発して適用していくことが重要であることを示しているという。そして研究チームは、誤り耐性量子コンピュータが確立するまでの間、どのようにNISQデバイスを基礎・応用研究に活用していくかという問題に指針を与えるものとしている。