東北大学とCUSICの両者は9月28日、結晶構造が立方晶の「3C-SiC」と六方晶の「4C-SiC」という、異なる結晶構造・物性値を持つシリコンカーバイド(炭化ケイ素)を積層させたハイブリッド構造基板を、新開発の「同時横方向エピタキシャル成長法」(SLE法)を用いて製作することに成功したと共同で発表した。

同成果は、東北大 電気通信研究所の櫻庭政夫准教授、同・佐藤茂雄教授、東北大 未来科学技術共同研究センターの長康雄特任教授、CUSICの共同研究チームによるもの。詳細は、9月18~22日にイタリアで開催された国際会議「ICSCRM2023」などにおいて口頭発表された。

パワー半導体の電力損失低減や長期信頼性の観点において、基板に用いるSiC単結晶が持つ物性そのものに由来する根本的な問題点が指摘されており、それらを克服する新しい技術の開発が待ち望まれていた。

そうした中でCUSICが、電力損失低減と長期信頼性確保を同時に実現する技術として考案したのが、パワー半導体デバイス「CHESS-MOS」だ。同デバイスは、結晶構造が立方晶の3C-SiCと六方晶の4C-SiCを積層させたハイブリッド構造基板である点を特徴とする。3C-SiC層には長期にわたって安定的に多くの電子を速く移動させる役割が、そして4H-SiC層には高い電圧に耐える役割が割り当てられており、これによって電力損失低減と長期信頼性を両立するという。

ただしその実現にあたっては、両SiCの結晶格子をシームレスに積層させるための新しい基板加工技術と結晶成長技術を開発する必要があった。そこで研究チームは今回SLE法を開発し、それを用いてCHESS-MOSを製作することに成功したとする。

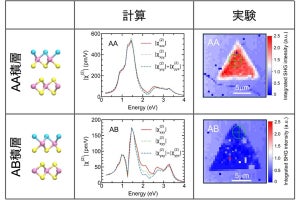

SLE法は、4H-SiC基板から延伸する4H-SiC基底面の上面に3C-SiCが結晶成長し、その3C-SiCもまた4H-SiC基底面に沿って延伸するという原理を利用しているので、3C-SiC層と4H-SiC基板の界面が1原子分の高さの狂いもなく平坦に形成されることが特徴だ。そのため、3C-SiC層内の自由電子は界面近傍を散乱されることなく高速に移動できるようになり、電力損失低減と高速動作につながることが期待されるという。

そこで走査型非線形誘電率顕微鏡法を用いて、絶縁膜(熱酸化膜)を形成したハイブリッド構造基板表面の界面準位密度の計測が行われた。すると、3C-SiC表面の密度は4H-SiC表面の200分の1以下となり、SLE法によって界面準位密度を大幅に低減できることが実証された。この低い界面準位密度であれば、過去のパワー半導体デバイス製作から得られている知見を参照すると、CHESS-MOSを取り入れることにより、電力損失が30%以上削減できる見通しとなるとした。

また3C-SiCが4H-SiCよりも大きな電子親和力を有することから、CHESS-MOSの絶縁膜/SiC界面に形成される電子に対する障壁は、4H-SiCよりも圧倒的に高くなることが考えられるという。それにより、絶縁膜を通して漏洩する電流密度は激減し、絶縁膜が短期間で劣化してしまう恐れがなくなり、SiCパワー半導体デバイスの長期信頼性が大幅に向上できるとした。

さらに、SLE法の実験において、3C-SiC/4H-SiC/3C-SiC/4H-SiCのような二重量子井戸構造が形成される現象も確認されたとする。このようなSiC積層構造を意図的に形成することにより、これまで、SiC半導体デバイスでは困難であると考えられてきた高周波デバイスを実現できる可能性も出てくるとした。

それらに加え、SLE法で半絶縁4H-SiC基板上に3C-SiC結晶を成長させることで、半導体基板との静電結合による高周波信号減衰の問題を回避できるため、既存のSiCパワー半導体デバイス生産ラインを用いた高周波集積回路の量産への道も開かれるとする。

-

SLE法により、3C-SiCと4H-SiCを積層させたハイブリッド構造基板(上)の基板表面の電子顕微鏡画像、(下)断面構造の概略図(基底面に対して基板表面は傾いているが、概略図ではわかりやすくするため、実際より傾きが強調されている)(出所:東北大プレスリリースPDF)

SiCを基板に用いると、シリコンに比べて熱や放射線に起因する誤動作や故障が起こりにくいことが知られている。今回の成果によりSiCの集積回路への応用の道が開かれるならば、高温や放射線にさらされる宇宙空間や原発廃炉作業場などの過酷な環境でも、誤動作や故障が生じにくい集積回路の実現につながることが期待されるとした。

またSLE法は、これまで構築されてきたSiCパワーMOSFETデバイスの形状や製造プロセスを大きく変更することなく、SiC基板表面の一部に異なる結晶構造を導入できる点が特徴であるため、多くのSiCパワー半導体デバイスの生産ラインに導入されることが期待されるとしている。