人でいっぱいの大きな部屋にいると想像してみてください。そこにいる人たちはあなたが必要とする重要な情報を持っています。皆はそれぞれ知っている情報を喜んで教えてくれますが、全員が一斉に話すため、部屋に人が密集すればするほど、周囲の雑音からあなたが集中して聴こうとしている人の言葉を聞き分けることが難しくなります。

この問題はクロストークと呼ばれ、Wikipediaでは「システムの回路またはチャネルに伝送される信号が、別の回路またはチャネルに望ましくない影響を与える現象」と定義されています。何十億個ものDRAMセルやトランジスタが非常に近接しているメモリやロジックデバイスの製造に携わっている方は、おしゃべりな人が大勢いる部屋とよく似た状況に直面していることでしょう。

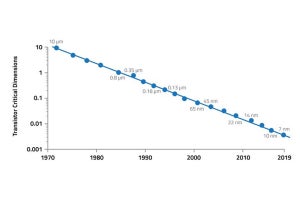

標準的なDRAMセルについて考えてみましょう。DRAMセルは、電荷の有無で1か0を表すキャパシタ、アクセストランジスタ、キャパシタの電荷状態を読み取るビット線で構成されています。技術世代ごとに高密度、高速化、消費電力の最小化が図られ、これらの構造は微細化され、近年では3D設計に進化しています。それと並行して、検出電圧(ΔV)とセル容量(Cs)の両方が世代ごとに減少しているため、ビット線の容量(CBL)も同じように減少させる必要があります。

「大勢の人がいる部屋」の例えでは、これらの減少は、あなたが聴こうとしている人があいまいな話し方をするため、言葉を聞き分けるのが一層難しくなる状態です。また、ロジックデバイスでも同様で、寄生容量(ゲート間とゲートとゲートコンタクトの間)が大きくなるにつれ、クロストークのリスクが増しています。

クロストークは、電子工学が生まれた当初から存在していますが、幸いなことにその対策には絶縁というよく知られている方法があります。混みあった部屋で、それぞれの人の周りに遮音板を置くといったところでしょうか。ICでは多くの場合、適切な絶縁膜で対応します。

この場合の「適切な」が指すのは、誘電率(k)を下げることだけではありません。これも重要な要素ですが、他の回路素子を損傷させるリスクなく成膜し、後ろの工程の熱処理、エッチング、クリーニングなどのプロセス後も膜の特性を保持できなければなりません。また、欠陥がなく均一である必要があります。さらに、この3D回路の時代では、厚さの均一性だけでは不十分です。垂直方向への成膜時も、膜の特性が均一でなければなりません。

その他にも考慮すべき要因があります。先進的な半導体メーカーは過酷な競争に直面しており、歩留まりを上げ、性能を向上させるために、独自の方法を開発しようと努力しています。これらの工程を担当しているエンジニアは、使用している膜の多用途性と柔軟性のメリットを活かしたチューニングを行っています。つまり、膜の組成を調整し、エッチング選択性などのさまざまな特性を実現する性能です。さらに、新世代のテクノロジーが高密度化と複雑化を重ねるごとに、こうした性能や歩留まりを向上させることはますます困難になっています。ここでもう一度「大勢の人がいる部屋」に例えてみると、部屋は小さくなるのに人々の声はもっと大きくなるということです。分離する必要性は高まっているのに、そのためのスペースがないということになります。

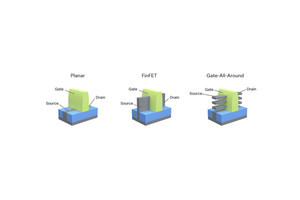

3D化する前は、絶縁法を模索するプロセスエンジニアとインテグレーションエンジニアは、チューニング可能な平面絶縁膜やコンフォーマルなSiO2および窒化物を成膜するのに十分に実証された技術を当てにすることができました。しかし今日では、チューニング性とコンフォーマル性の他に、シリコンオキシカーバイド(SiCO)などのSi-C結合を含む膜の性能も求められています。これらは、エッチングの選択性を高めるために必要で、ゲート・オールアラウンド(GAA)型スペーサから、BEOL絶縁膜や高度な露光工程に至るまで、さまざまな用途で重要性が増しています。それと同時に、プラズマが回路機能に与える損傷についての懸念も高まっています。

それでは、絶縁性の探求を進めるにはどうしたらよいでしょうか? 1つの解は、これらの新しいニーズに対応した新成膜技術である「SPARC」です。高アスペクト比の構造でも深さ方向に均一な組成と膜特性を維持できることに加えて、SPARCはコンフォーマルなSiCO薄膜を可能にし、ロジックデバイスでもDRAMデバイスでもLow-Kスペーサとして使用する際に効果的な絶縁性を実現します。

SiCO成膜の系列中でも、SPARC法は多様な組成チューニングを可能にしながら、卓越したコンフォーマル性を実現しています。K値が約4~4.4でリークの少ない高密度で安定性の高いSiCO膜を、下層を酸化させることなくCoやWなどの金属に直接成膜できます。この膜は密着性に優れているだけでなく、密封性もあります。400℃という低い成膜温度でも、末端メチル基がほとんど、あるいは全くないために、炭素が完全に相互架橋し、他のSiOC膜に比べて熱的にも化学的にも安定しています。

重要なことは、これらはすべて非プラズマ環境の成膜で実現できることです。生成されたラジカルが、入念に選択された前駆体分子の特定の結合のみと反応します。すなわち、前駆体分子における結合の切断が選択的になり、付着係数が極めて低く、その結果として優れた段差被覆性を示す前駆体ラジカルが形成されます。Si-C結合は成膜時に切断されず、前駆体分子のシリコンに結合するO、NまたはCも保持されます。このような多様な組成チューニングを実現するために、前駆体の設計と選択は、目的の膜種によって異なります。

このプロセスでは、Si-O結合の密度を下げることでSi-C結合の比率を上げることができます。異なる温度で成膜された場合でも、膜に含まれる炭素の密度や総量よりも架橋した炭素の量が、エッチング選択性では重要になります。さらに、これらSiCO膜のウェットエッチングレート(WER)は、低濃度HFや高温リン酸などの一般的な薬液でゼロであるため、ウェットエッチングの選択比はほぼ無限大になります。また、ピンホールをなくすには少なくとも30Åの膜厚を必要とするALD法を用いたSiN膜と違って、15Å以下まで薄膜化が可能です。

ところで、実用上ではどうでしょうか? DRAMセルの例に戻りましょう。前述のとおり、セルの容量が減少し続けているので、検出能力(すなわち、「セルの声を聴く」能力)を向上させるために、ビット線の容量減少に対する要求に拍車がかかっています。

ビット線容量の大部分は、ビット線とストレージノードセル(SNC)間のカップリングに起因しています。20nmノードの世代以降、エアギャップの導入がこのカップリングを減少させる手段になっています。ここで留意すべき点は、空孔の両側は絶縁膜であり、コンフォーマル性、密着性、密封性、誘電率、耐圧など数多くの厳しい要求を満たす必要があるということです。SPARC法で成膜したSiOCの特性から、従来の材料よりも容量カップリングが低くなり、DRAMの性能が向上します。

ロジックデバイスでは、ゲート間でもゲートとゲートコンタクトの間でも寄生容量を低下させる手段として知られている技術にゲートスペーサがあります。このスペーサのコンセプトは、3Dゲート・オールアラウンド型(GAA)アーキテクチャに引き継がれましたが、スペーサの材料は、横方向のエッチストップ材として機能する必要があるという問題があります。

繰り返しになりますが、SPARC法で成膜したSiOC膜が示す特性は、この要求にまさにぴったり当てはまります。電気的性質に加えて、SiOCが持つ高い異方性とエッチング選択性が、他の技術よりも優れたパフォーマンスを実現します。

どちらの例でも、クロストークの最小化は数多くある懸念の1つに過ぎませんが、この最小化が回路設計の工程全体に大きな意味をもたらします。これによりキャパシタとトランジスタの負荷が緩和され、期待される機能を発揮しやすくなるからです。つまり、大局的に見れば、性能を向上させるために、コストや新たな複雑さを追加させる他の方法を考える必要がなくなるということです。これは、基本的なレベルの比較的小さな改善が、大きな影響を及ぼすことができる好例です。

SPARCプロセスの高い柔軟性と適応性により、コンフォーマルで多様な組成の成膜が可能になります。例えば、高いレベルのチューニング性によって、シリコン炭窒化(SiCN)膜の成膜にも適用できます。炭化ホウ素(BC)や窒化ホウ素炭素(BCN)などの高品質でコンフォーマルなホウ素ベースの膜も問題なく成膜できます。これらの膜は、Siベースの膜とは異なるスパッタリングやエッチングの挙動を示します。

特に興味深い可能性は、複雑さが増す3D構造の製造に向けて開発されているSAQP(Self-Aligned Quadruple Patterning)やSAGC(Self-Aligned Gate and Contact)、fSAV(fully Self-Aligned Via)などの高度な加工技術への応用です。これらはすべて、新たなレベルの位置合わせ精度を実現するために、高いエッチング選択性を持つ材料に依存しています。基本的に、さまざまなプラズマエッチングおよびウェット薬液において、互いにほぼ完全なエッチング選択性を示すスペーサー、ハードマスク、およびエッチングストップ材(平面およびコンフォーマルの両方)の独自の組み合わせが必要になります。BCおよびBCNをベースにした膜は、適切なk、コンフォーマル性、電気的特性などの性能を示すため、ふさわしい候補となります。

同様に、SPARC法で成膜した炭化ケイ素(Si-C)ベースの膜は、酸化物や窒化物に対して適切な選択性やチューニング性を示すため、3D NANDメモリホール加工に使える可能性があります。また、プラズマべースの処理が問題を起こす状況では、ラジカルによる成膜により、新たな選択肢が実現するでしょう。

半導体製造ほど急速に進化している産業は他にほとんどなく、変化し続ける製造工程の開発とインテグレーションが常に課題となっています。半導体業界が3D化などの新たな課題や、クロストークなどの長期的な問題に直面し続ける中、これらに対応するために創意工夫と創造性が求められ、そして「各種情報をはっきりと聞き取れる」ようにするために、SPARCのような革新的な技術が必要になるでしょう。