米国の半導体製造装置メーカー大手KLAは、最先端プロセスを採用したロジック半導体ならびに半導体メモリの製造歩留まりを向上させることを可能とする検査装置として、パターン無しシリコンウェハ表面欠陥検査装置「Surfscan SP7XP」と回路パターン付きウェハ形状計測システム「PWG5」を発表した。

Surfscan SP7XP

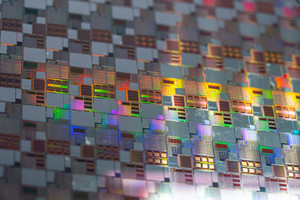

先端ロジック領域では現在、EUVを多用した5nmデバイスの量産化が進んでいる。EUVリソグラフィは、これらの先端プロセスで活用されているが、そうした微細かつ複雑なパターニングを繰り返し高歩留まりで製造を行うためには、パターン無しウェハの表面欠陥検査を慎重に行って、製造装置やプロセスを頻繁に監視したりするなど、精密な欠陥管理が必須となっている。

Surfscan SP7XPは、これまでのウェハ表面欠陥検査増値「Surfscan SP7」を高感度化したモデルで、高感度化に加えスループットの向上も実現したほか、機械学習ベースの欠陥分類を導入することで、より幅広い種類のブランケットフィルムや基板上の欠陥を捕捉し、識別することが可能になったという。また、スループットを犠牲にして高感度を得るための12.5nm検出モードも搭載されたという。

KLAのSurfscanおよびADE部門のゼネラルマネージャーであるJijen Vazhaeparambil氏は、「Surfscanの設計チームは、感度と欠陥分類に対応する技術の進歩だけでなく、CoO(Cost of Ownership)の改善にも重点を置いた。この結果、Surfscan SP7XPは、研究開発から最先端のデザインノード基板やデバイスの大量生産までをカバーする、パターン無しウェハ検査として使用できるようになった」と述べている。

PWG5

一方のPWG5は、高解像度でウェハジオメトリの微細な歪みを測定することで、パターン付きウェハの歪みを識別することを可能とする装置。例えば3D NANDでは、複数の材料を用いた薄膜を幾重にも繰り返し堆積させメモリセルを作製する必要があるが、積層数が増えれば、ウェハに応力が発生し、最終的にはウェハに歪みが発生し、平坦度が悪化。歪みのあるウェハは、下流プロセスの均一性とパターニングの完全性に影響を与えることとなり、最終席にはデバイスの性能と歩留まりにも影響をおよぼすこととなる。

「3D NANDの複雑な構造の多層化は、ウェハの反りを顕著にし、その形状を測定することが求められるようになった。PWG5は、ウェハの表側と裏側の平面性からの偏差を同時に測定することを可能としており、3D NANDだけでなく、DRAMやロジックでも活用できる。また、KLAのデータ分析システムと組み合わせることで、ウェハの再加工、プロセスツールの再キャリブレーション、リソグラフィシステムへの警告などの意思決定を促進し、可能な限り最良のパターン補正を適用できるようになっている」とVazhaeparambil氏は述べている。