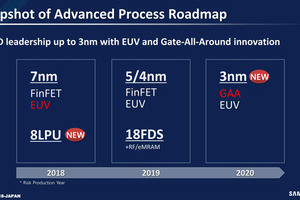

Samsung Electronicsが、5nmプロセスの開発完了と併せて6nmプロセスの提供を発表したばかりだが、先行して5nmプロセス向け設計基盤の提供開始を発表していたTSMCが、7nmと5nmをつなぐ6nmプロセス(N6)を発表した。同6nmプロセスは、7nm向けの設計から直接移行できる点が売りで、コスト対性能の観点で高い競争力があり、付加価値の高い新製品の迅速な市場投入を可能にするとしている。

TSMCは現在、EUVリソグラフィを採用した7nmプロセス(N7+)のリスク生産を行っているが、そのEUVリソグラフィプロセスで得た知見をN6にも適用することで、既存の7nmプロセス(N7)比で、ロジック密度を18%向上することができるという。また、デザインルールは従来の7nmプロセスと互換性があり、その包括的なデザインエコシステムを再利用して開発することができるため、少ないエンジニアリングリソースで、短時間で設計を変更することが可能だとしている。

N7+では、ごく限られた工程にEUVリソグラフィを適用する一方、5nmプロセスでは本格的に採用するため、ArF液浸リソグラフィによる多重露光プロセスの工程数が減ることとなる。そのため、設計データをそのまま活用することは難しく、大きく手直しをする必要がでてくるが、N6では、7nmプロセスの設計データをほぼそのまま活用できるとTSMCでは説明している。

このN6については、主にハイエンドからミドルレンジのモバイル、コンシューマ製品、AI、ネットワーキング、5Gインフラストラクチャ、GPU、および高性能コンピューティング向けロジックデバイスに使われることが想定されており、N7プロセスを活用している多くの顧客が活用することが期待できると同社では見ている。

なお、N6プロセスについては2020年第1四半期にリスク生産を開始する予定としており、これによりTSMCは、7nmに続き、6nmおよび5nmプロセスでもファウンドリ事業の拡大を目指すSamsungと激しい先頭争いを繰り広げることが予想される。