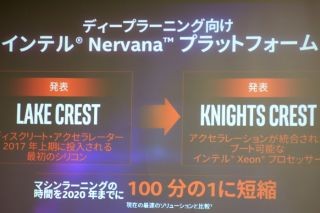

IntelのSpring Crest

「Spring Crest」はIntelが買収したNervana社が開発していたマシンラーニングのトレーニング用チップを製品化したものである。

ディープラーニングモデルの学習は計算量が多く時間が掛る。実世界では学習にかかる時間と電力効率が重要となる。そして、使われるモデルの大きさと学習に使われるデータセットの大きさは3.5カ月ごとに倍増しているという。

ディープラーニングでは行列積の計算と畳み込みの計算が大部分を占める。ディープラーニングのアクセラレータでは、消費電力、計算性能、メモリと通信、スケールアウトの能力が主要な評価項目となる。

-

ディープラーニングでは行列積と畳み込みが主要な計算である。ディープラーニングのアクセラレータの評価では、消費電力、計算性能、メモリと通信、スケールアウト能力が主要な項目である (出典:この連載のSpring Crestの部分のすべての図はIntelのAndrew Yang氏の発表スライドのコピーである)

Spring Crestのアーキテクチャ設計方針は、大きなモデルやデータセットが扱えるようにし、与えられた電力枠の範囲でネットワークの学習をできるだけ短い時間で行うことである。そのためには、計算と通信とメモリの処理時間をバランスさせることが重要である。さらに、すでにチップ上にあるデータをできるだけ再利用すること、バッチにまとめられたワークロードの処理を最適化することが重要である。そして、スケールアウトのサポートを組み込んで置くこと、将来のワークロードもサポートできるようにすることも重要である。

なお、Spring Crestに(NNP-T)と書かれているのは、Neural Network ProcessorでTはTraining用であることを表している。

-

Spring Crestの設計方針は、大きなモデルやデータセットが扱え、与えられた電力枠のなかで学習時間を最短にするというものである。また、スケールアウトで、より大きなモデルやデータセットが扱え、将来のワークロードもサポートできることが求められる

Spring Crestは24個のTensorプロセサを持ち、最大演算性能は119Topsで、60MBのオンチップメモリを持っている。そして、4個のHBMが接続されている。I/O接続にはPCIe Gen 4を16レーン備えている。

-

Spring Crestは24個のTensor Processorを搭載し、ピーク演算性能は119Tops。メモリは4個のHBMを接続している。Tensor Processorの内部に合計60MBのメモリを持っている

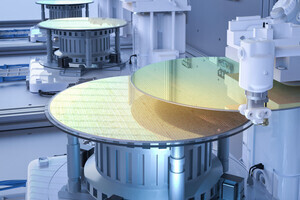

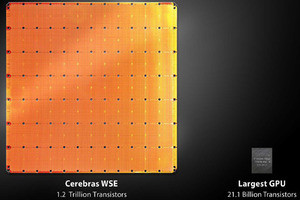

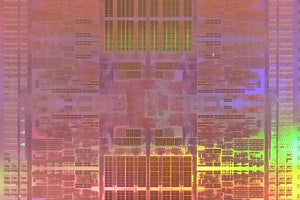

Spring CrestはTSMCの16FF+プロセスで作られ、チップサイズは680mm2で270億トランジスタを集積し、4個のHBM2-2400メモリを含めて1200mm2のインタポーザに搭載されている。64レーンのSerDesを搭載し、全体のI/Oバンド幅は3.58Tbpsに上る。

Spring Crestコアのクロックは最大1.1GHzで、典型的なワークロードでの消費電力は150~250Wであり、空冷で冷却している。

次の図の中の3つの写真は左上がダイ写真、右上が60mm×60mmの3352ピンのBGAパッケージに搭載されたSpring Crestチップ。下の写真はNICを接続したモジュールの写真である。

-

Spring CrestはTSMCの16FF+プロセスで作られ、チップサイズは680mm2で270億トランジスタを集積する。コアクロックは最大1.1GHzで、通常負荷状態の消費電力は150-250Wで空冷である

ソフトウェアスタックは、ハードウェア(図には書かれていない)の上にボードファームウェアとチップファームウェアがあり、その上にカーネルモードドライバが載っている。その上にDNNのカーネルライブラリのArgonが載っている。さらに、ハードウェア依存性のないディープラーニング用ライブラリで、コンパイラも含まれているnGraphが載っている。そして、その上にはTensorFlow、PaddlePaddle、Pytorchなどが乗るというスタック構造になっている。

-

ハードウェアの上にボードとチップのファームウェアが載り、その上にDNNの計算や通信のカーネルライブラリが載り。さらにその上にハード依存性のないディープラーニングライブラリやコンパイラを含むnGraphが載るというスタック構造になっている。nGraphの上ではTensorFlowやPaddlePaddle、Pytorchなどが動作する

計算エンジンであるTensor Processing Cluster(TPC)のブロックダイアグラムを次の図に示す。TPCは32×32の乗算器アレイを2個と畳み込み計算エンジンを持つ。それに加えて多数のローカルメモリバンクを持っている。 右上の部分はメッシュネットワークを構成するルーターである。

(次回は9月18日に掲載します)