Samsung(Photo05,06)

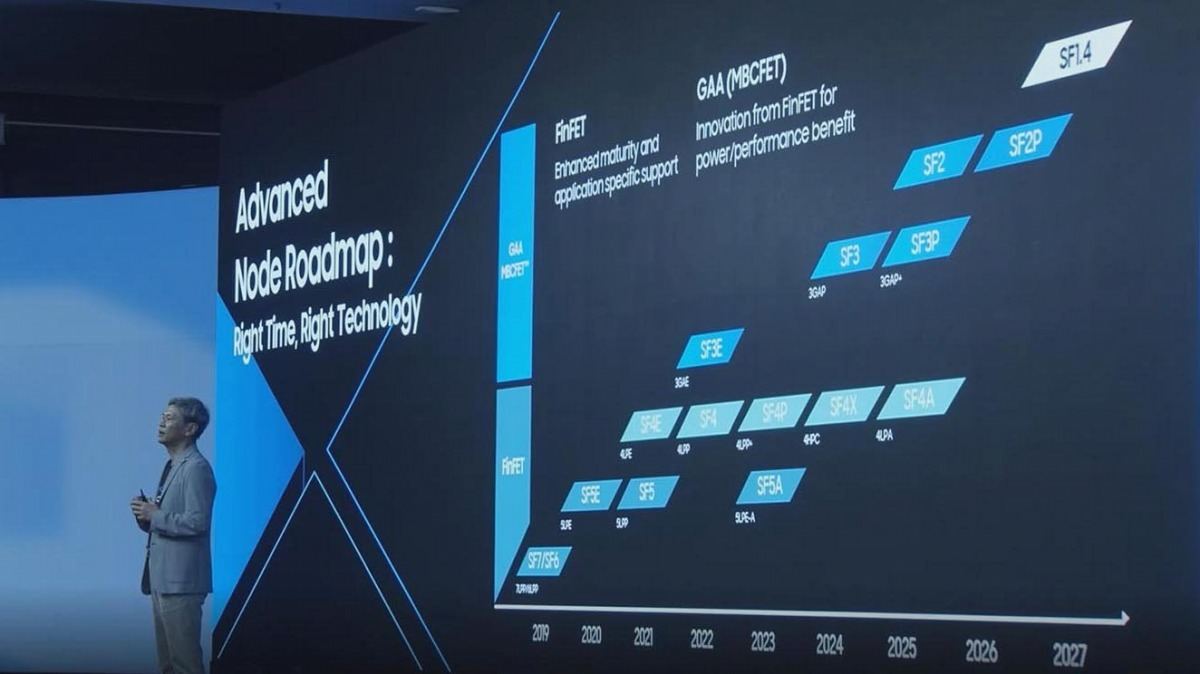

こちらのレポートでも書いたが、今年Samsungはノードの名前を全部変えてしまったため、判り難い事おびただしい。先の記事は、Samsung提供の写真を実物大で掲載したのだが、元が小さすぎて非常に読みにくい。ただその後SFF(Samsung Foundry Forum)2022がオンラインで視聴可能となったので、こちらのスライドを改めて示す。ということでロジック向けプロセスはこんな具合(Photo07)。ちょっと判りくいので改めて整理すると

| 2019年 | SF7 | 旧7LPP |

|---|---|---|

| SF6 | 旧6LPP | |

| 2020年 | SF5E | 旧5LPE |

| 2021年 | SF5 | 旧5LPP |

| SF4E | 旧4LPE | |

| 2022年 | SF4 | 旧4LPP |

| SF3E | 旧3GAE | |

| 2023年 | SF5A | 旧5LPE-A |

| SF4P | 旧4LPP+ | |

| 2024年 | SF4X | 旧4HPC |

| SF3 | 旧3GAP | |

| 2025年 | SF4A | 旧4LPA |

| SF3P | 旧3GAP+ | |

| SF2 | ||

| 2026年 | SF2P | |

| 2027年 | SF1.4 |

ということになる。5LPE-Aとか4LPAなどはこれまで聞いたことが無かったのだが、多分内部的に改良を加えたバージョンであろう。で、3nm以下がGAA、4nm以上はFinFETである。さて、既にSF4というか4LPPまでは量産がスタートしている。もっともこのSF4を使うクライアントが現時点では不明である。以前はQualcommのSnapdragon 7 Gen 2が4LPPを使うという話だったが、最新情報ではこれがTSMCのN4になった、という噂が流れている。あと、昨年書いた「AMDがローエンドCPUをSamsungに委託する」という話もガセだったようで、少なくとも現時点ではそうした動きは一切ない。

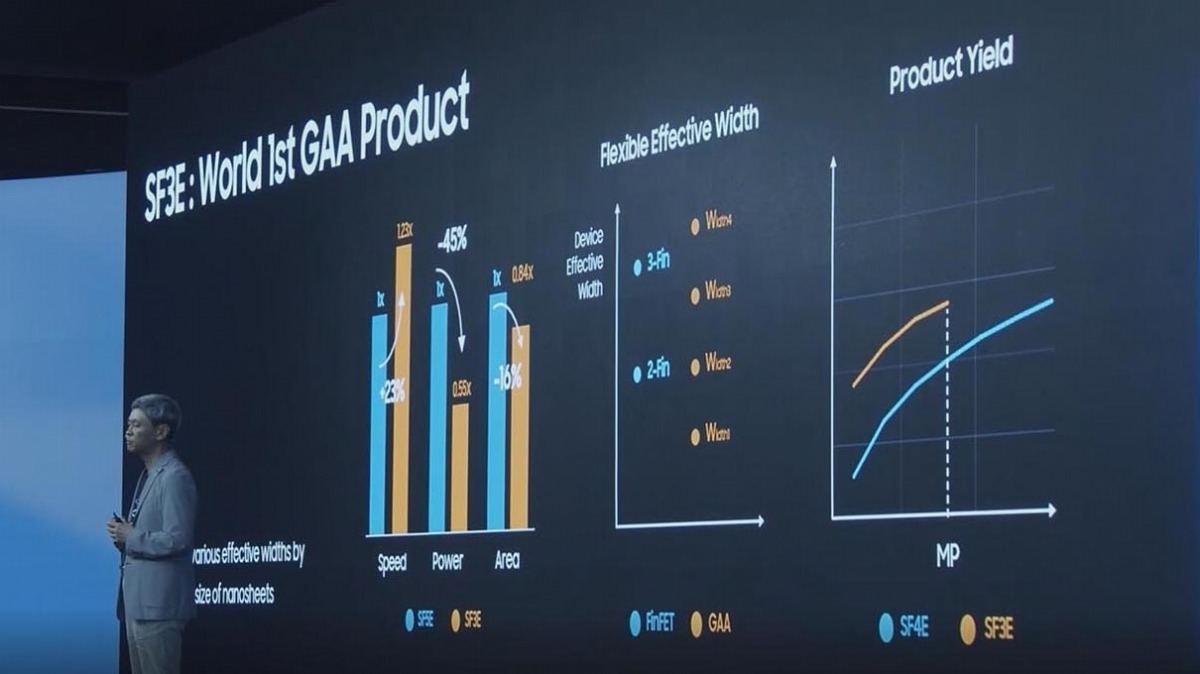

さて、FinFETプロセスについては昨年の記事以上の情報が無いので、GAAの方を。Samsungは2022年6月30日にGAAプロセスの量産開始を発表した。これが3GAE、今の言い方で言えばSF3Eである。このSF3E、説明によれば5nmプロセス(SF5?)と比較して同一周波数で45%省電力、同一消費電力なら23%高速に動作し、エリア面積を16%削減できるとしている。速度/消費電力はともかくトランジスタ密度はあまり向上しないのが不思議だが、説明によれば第2世代GAA(つまりSF3/3GAP)では消費電力50%削減又は動作周波数30%向上が期待でき、エリア面積は35%削減できるとしている。その意味でも本命は2024年の3GAPというかSF3ということになる。

実際このSF3Eは量産開始と言いつつ、歩留まりが30%未満だとか20%を切っているという話が伝わってきており、そりゃここまで歩留まりが悪かったら本格量産にはとても耐えないだろう。100平方mm程度のモバイル向けのダイはともかく、GPU向けの300平方mm~600平方mmのダイだと、下手をするとウェハ1枚から数個とか、1個も取れないとかの可能性すらある歩留まりだからだ。

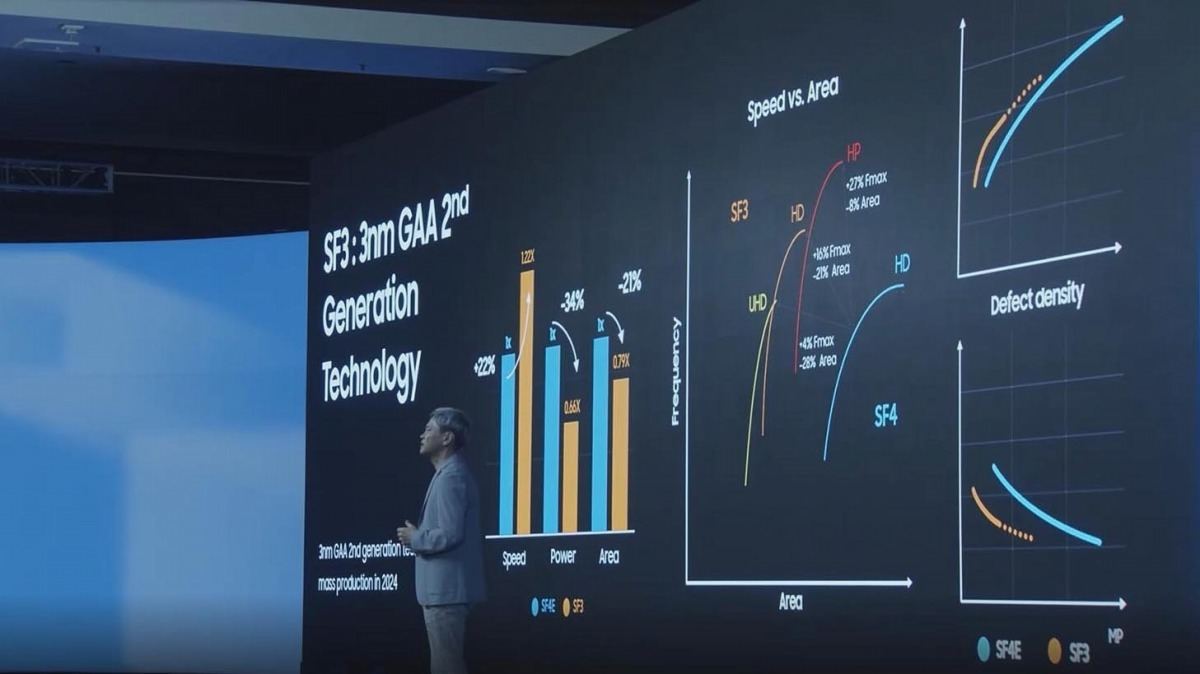

ただSFFではそのSF3Eのパラメータが改めて示され(Photo08)、歩留まりもSF4Eよりはずっと良いとされた。ただ先の噂が本当だとすると、SF4Eは更に歩留まりが悪かったということになる。Photo09は恐らく本命であるSF3のパラメータで、SF4Eと比較してこちらも悪くない歩留まりや欠陥レートだとするが、比較対象が悪すぎる気はする。ただそれはともかくとして、SF3ではHP/HD/UHDの3種類のライブラリがあり、どれを利用するかで動作パラメータが変わってくる事が示されているのは興味深い。

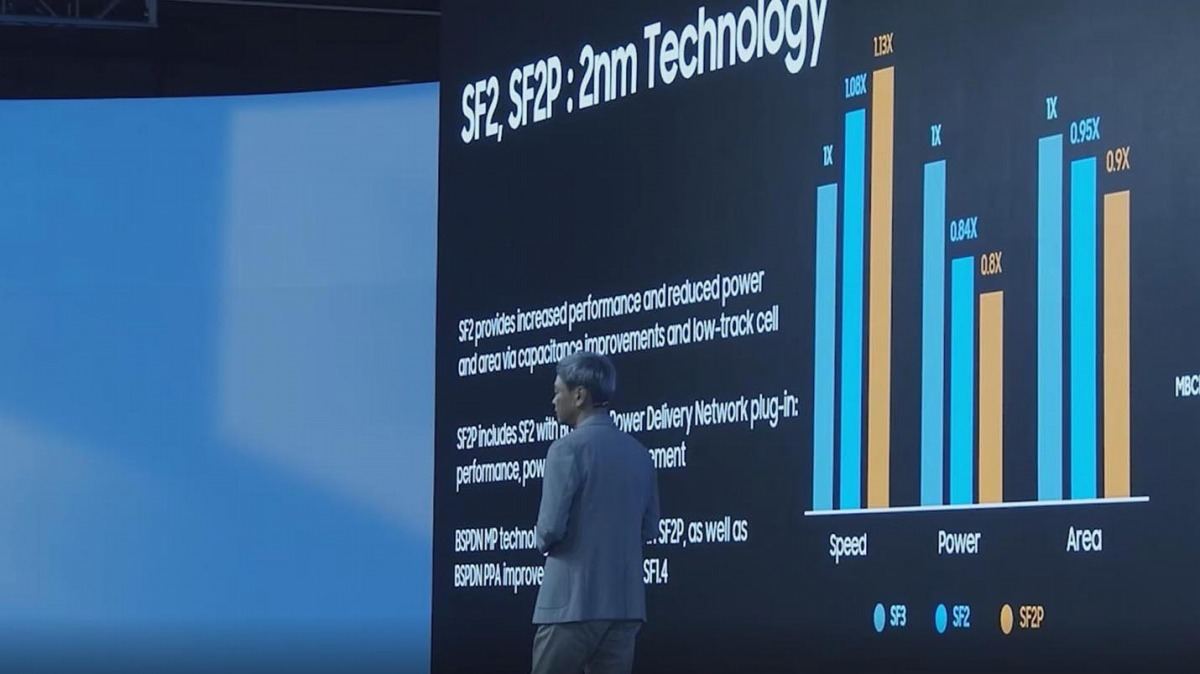

またその先のSF2/SF2Pについてもパラメータが示されている(Photo10)。SF2Pだと、SF3比で速度13%向上または消費電力20%減、それとエリアサイズ10%減が実現できるとしている。個人的には、意外にエリアサイズ削減が難しいのだなというのが正直なところ。恐らく今回は一切詳細が開示されなかったSF1.4でもエリアサイズ削減の効果はそれほど無く、根本的にはCFET(Complementary FET:PMOSとNMOSのトランジスタを縦に積層する)が登場するまで微細化は暫く緩やかになりそうな感じだ。

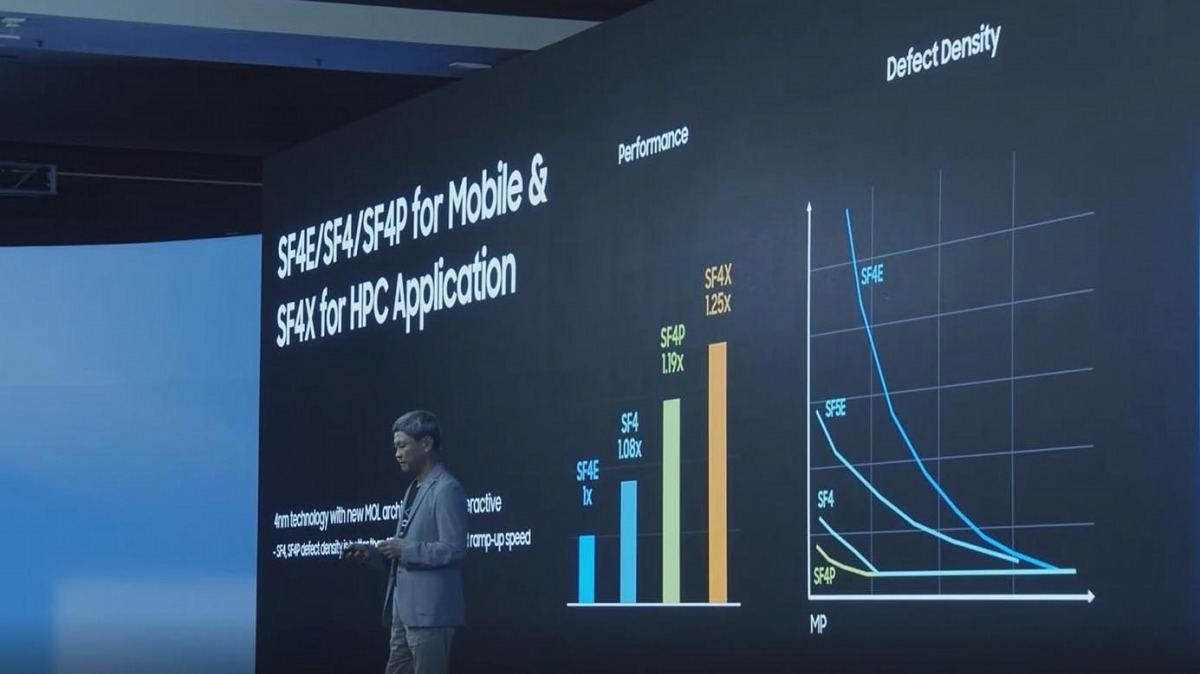

ところでGAAとは別に、Samsungは引き続きFinFETプロセスも進化させてゆく、としている(Photo11)。どちらかというと、直近はこちらの方がユーザーが多そうではあるのだが、こちらはエリアサイズの削減効果はあまり期待できなそうだ。ただSF4XだとSF4Eから25%動作周波数を上げられる、というのはそれなりにアプリケーションが見つかりそうではある。

-

Photo11: 右のグラフを見るとSF4は非常にDefectが少ない筈なのだが、もう縦軸が不明なのでなんとも言えない。とりあえずSF4EのDefectの高さを見ると、SF3EがSF4Eよりマシというのは理解できるが、SF4EのYieldはどの程度なのだろう?

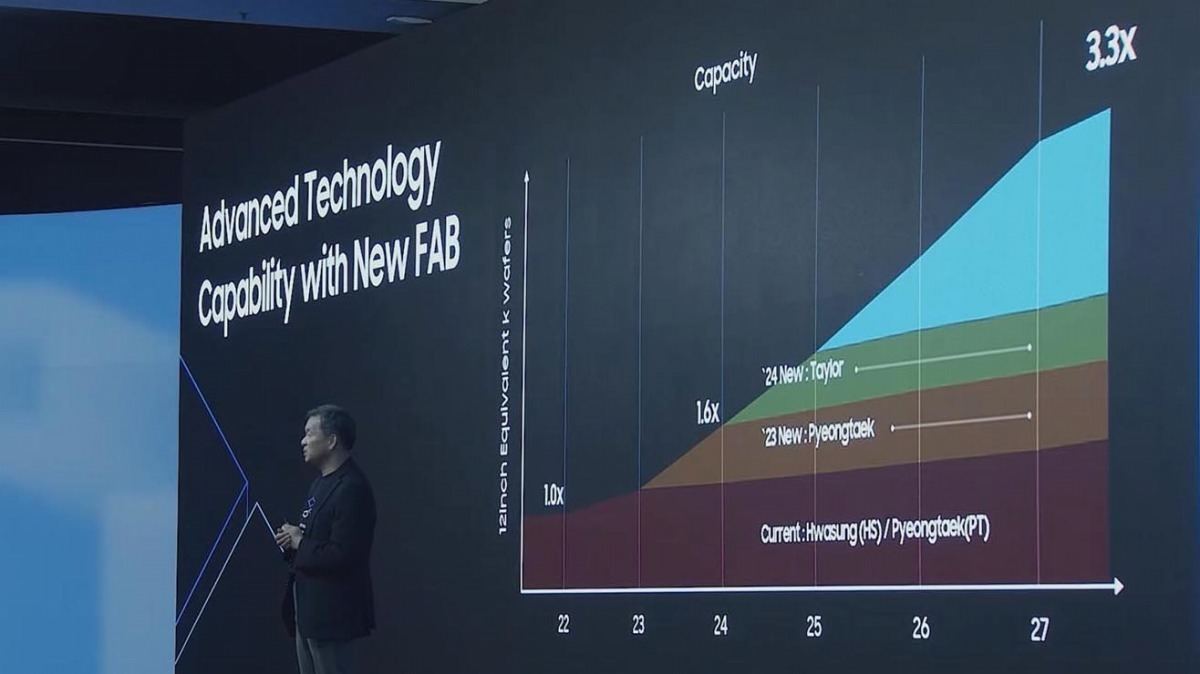

SFFでは他に自動車向けプロセスとかRF、特殊用途向けプロセスなども紹介されたが、こちらは今回は割愛するとして最後に生産能力について。Samsungの計画では、2022年比で3.3倍の生産能力を2027年には達成する、としている(Photo12)。同社は韓国に3拠点を持っており(Photo13)、それぞれ

GH:Giheung Campus 6 Line/S1 Line

HS:Hwasung Campus S3 Line/S4 Line

PT:Pyeongtaek Campus S5 Line Phase 1/S5 Line Phase 2

となっている。また米国ではテキサス州のAustin CampusにS2 Lineを保有しているが、2022年11月に170億ドルを投じてテキサス州のTaylorに新しいFab(S6 Line?)を建設する事を発表している(Photo14)。これだけ生産能力を拡大するとなると、当然それだけモノを作らなければ投資は回収できない訳で、なので今後Samsungはこれまで以上に積極的にセールスに力を入れることになる。当然そこにはPC向けも含まれるわけで、メインストリーム~バリュー向けGPUとかバリュー向けCPUなどもそのターゲットになるかと思われる。ただ、2023年中にそれがマーケットに見える形で出てくるかどうかは怪しいところで、早くて2024年以降になりそうに思う。