新年の幕開けに、パーソナルコンピュータのハードウェア技術の動向を占う「PCテクノロジートレンド」をお届けする。本稿はCPU編だ。2020年に苦戦が見られたIntelと、対照的に好調だったAMDが、2021年にはどんなCPUロードマップを描いているのかが非常に興味深いところだろう。

|

◆関連記事リンク (2021年1月1日掲載) PCテクノロジートレンド 2021 - プロセス編 (本稿) PCテクノロジートレンド 2021 - CPU編 (2021年1月3日掲載) PCテクノロジートレンド 2021 - GPU編 (2021年1月4日掲載) PCテクノロジートレンド 2021 - メモリ編 (2021年1月5日掲載) PCテクノロジートレンド 2021 - チップセット編 |

|---|

***

Intel CPU

Processのところでも述べたように、2020年は14nmプロセスをやりくりし、なんとか10コアのComet Lakeを投入して凌ぎはしたものの、凌ぎきれずに次第にシェアを落としていった、というのがDesktop向け。一方でモバイル向けはIce Lakeが今一つ伸び切らず、Comet Lakeとの二本立てという形で何とかこらえた苦労の年でもあった。まぁTiger Lakeの投入で多少は持ち直した感はあるのだが。

-

Photo01: 茶とらん坊。もとは知人が保護し、一時預かりさんに預けていていたらそこの先住に虐められて脱走。再保護してウチが一時預かりPart 2をしていた子。ただその後ちゅるる女王様になついて、なし崩しに大原家の猫に。ビビりで人間が怖くてしょうがなかったのが、次第に慣れてきたのは可愛かった。ただ病気(多分梗塞か何か)をして、再び人間が怖くなってしまったり、色々難儀な子であった。2016年4月逝去。

(編集注:「PCテクノロジートレンド」では例年、記事中に度々"猫"が登場することがあります。これは、著者の助手(?)をつとめる猫たちが仕事を手伝う(?)様子を節目として差し込むことで、複雑な話題を読み解きやすくする効果を狙った演出かもしれません)

さてそのIntel。まず2021年の第1四半期にはRocket Lakeを投入する。恐らくCESの前後でまずアナウンスがあり、製品投入は3月といったところになるだろう。Rocket Lakeで現状判っている情報は以前こちらで説明した通りである。コアはWillow Coveを14nmに移植しなおしたCypress Coveであり、最大8コア。またGPUはXe-LEベースとなる。PCIe Gen4のサポートやDDR4-3200のサポートなども追加され、これでやっとAMDのZen 2/Zen 3とスペック上は並ぶことになる。

さて、ではこれでComet LakeはRocket Lakeに交代か? というとそういう訳でもなく、引き続きRocket Lakeは併売されるらしい。そもそもRocket Lake及びこれに組み合わせるIntel 500チップセットがいわばワンポイントリリーフ的な扱いだからだ。もともとIntelは2021年にAlder Lakeベースのコアを搭載することを明らかにしている。このAlder Lakeであるが、LGA1700のパッケージになる事が、Intelの情報で事実上明らかである。ということで、何時になるのかははっきりしないがAlder Lakeベース製品の投入時にはまたプラットフォームが変わる事になる。多分上から下までラインナップを刷新するのは、このAlder Lakeの投入時となると思われる。とりあえずRocket LakeはZen 3ベースのRyzen 5/7/9への対抗馬という位置づけであり、PentiumやCeleronに加えてCore i3に関しても、引き続きComet Lakeのままになると思われる。

そのRocket Lake、細かなスペックなどは勿論現時点では不明だが、TDPに関しては面白い話題が流れてきている。Intelの場合、消費電力はTDPだけでなくPL1(=事実上のTDP)とPL2を考慮する必要があるというのは昨年記事にしたが、Rocket LakeのハイエンドであるCore i9-11900Kの場合はPL1 125W/PL2 250WでComet Lakeと変わらないが、その下のCore i9-11900ではPL1が65Wなのに対しPL2は224Wに設定されているらしい。元々Comet Lakeに比べるとコアそのものが複雑化して消費電力が増えている関係で、ベースの動作周波数は抑えめにして、その分Turbo時にぶん回すことで性能を確保するという発想らしいが、ついにPL1とPL2の比が3倍を超えたようだ。なおPL1 Tauの値は不明である。なんというか性能評価をやると変動が大きそうである。それとGPUにはXeを搭載するとされているが、こちらは24EUと32EUのモデルが用意されるらしい。10nm SuperFinでトランジスタ密度を上げられるTiger Lakeはともかく、14nmだとあまりGPUの為にトランジスタを割けない、という事でこれは理解できるが、結果としてGPU性能はRyzen 4000Gシリーズに及ぶところまで行くかどうか、ちょっと怪しい感じだ。

ちなみにComet LakeはIntel 400シリーズとIntel 500シリーズの両方のチップセットに対応できる(ただしCPUから出る追加のPCIe x4には対応しないし、x16レーンもPCIe Gen3のまま、メモリもDDR4-2933までが正式対応)が、Rocket LakeはIntel 400シリーズでは動作しないと思われる。まぁこれに関しては致し方ないところだろう。

この後に続くのがAlder Lakeである。先のArchtecture Dayのスライドにもあるように、Golden CoveとGracemontのHybrid構成で、その意味ではLakefieldの後継という位置づけではあるのだが、実はBoyd Phelp氏へのインタビューの際に「そもそもAlder Lakeのポジショニングは? Lakefieldの後継のHybrid向けという事でいいのか?」と確認を取ったところ「Hybridという意味ではLakefieldの後継であるが、MobileからDesktopまで幅広い範囲でHigh PerformanceとLow Power Comsunptionを両立できる」という返事をもらっている。先にも触れたがIntelはAlder LakeベースのDesktop向けをLGA 1700で投入予定であり(Photo02)、なのでTigerLakeなどと異なりMobile向けとDesktop向けの両対応という形になる。ちなみに現時点においても、Gracemontのみのコアを使う製品のロードマップが聞こえてきておらず、ということはAlder LakeはComet Lake/Rocket Lake/Ice Lake/Tiger Lakeすべての後継になる可能性が高いということだ。

-

Photo02: これは2020年6月にark.intel.comで"Alder Lake"を検索すると出てきた結果。個別のドキュメントにはアクセスできないが、この検索結果だけで十分である。ちなみに現在はドキュメントが他の場所に移されたようで、検索しても何もでてこない。

製品ラインが一本化されるのは喜ばしいが、そうなると恐らくAlder Lakeで先行するのはMobile向けであって、Desktop向けは当然後になるだろう。これは10nm SuperFinの生産量にもよる部分だが、下手をすると2021年中はMobileのみで、Desktop向けは2022年までお預けの可能性もある(というか、その公算が高い)。本当であれば、2021年の第3~第4四半期に投入されるZen 4に向けてAlder Lakeをぶつけたいだろうが、それを実現するためのキャパシティが無く、外部Fabに今から委託も出来ない(出来たところでTSMCもそこまでのキャパが無い)以上仕方がないだろう。まぁそんな訳で2021年もIntel Desktop向けCPUは苦難の道のりと思われる。

これに比べると、モバイル向けは(まだIce Lake/Comet Lakeがそれなりに混じっており、ちょっと大変だが)Tiger Lakeの生産量が増えてゆけばまだまだ市場のシェアを握りやすい。ただこちらに関しても、2021年の前半にはAMDが現在のRenoirベースのRyzen 4000Gシリーズの後継としてCezanneベースの製品を投入予定である。こちらの詳細はこの後説明するが、これが出てくるとちょっとTiger Lakeも苦戦は免れないだろう。ただここで半年凌げばAlder Lakeが投入される訳で、Desktopよりはまだマシというところだろうか。

ついでにServerに関しても。Photo03はProcessのところでも出したスライドであるが、実を言えば

- Cooper Lake: 確かにごく一部には出荷されているものの生産量が非常に少なく、事実上大口カスタマー向け。なので現実問題としてはまだCascade Lakeがメイン。

- Ice Lake-SP: 2020年8月の時点では2020年中の出荷を目論んでいたが、第3四半期のEarning Callの中でSwan CEOは"we and our customers are excited about the upcoming launch of our 3rd Gen Xeon Scalable product, Ice Lake. We're targeting qualification at the end of Q4 with volume ramp shortly after in Q1."(我々と顧客の両方が待ち望んでいる第3世代のXeon Scalable、つまりIce Lakeであるが、検証を今年第4四半期中に終わらせ、来年第1四半期から量産を開始する)と述べた。要するにこれも1四半期スリップして2021年になったわけだ。おまけに、当初(2019年頃)の予定ではIce Lakeが1 Socket~8 Socketまで全部カバーする予定だったのが、現在では4 Socket以上は引き続きCooper Lakeが担い、Ice Lakeは2 Socket以下を担うという形になっている。

-

Photo03: Cooper Lakeの詳細はこちらに。

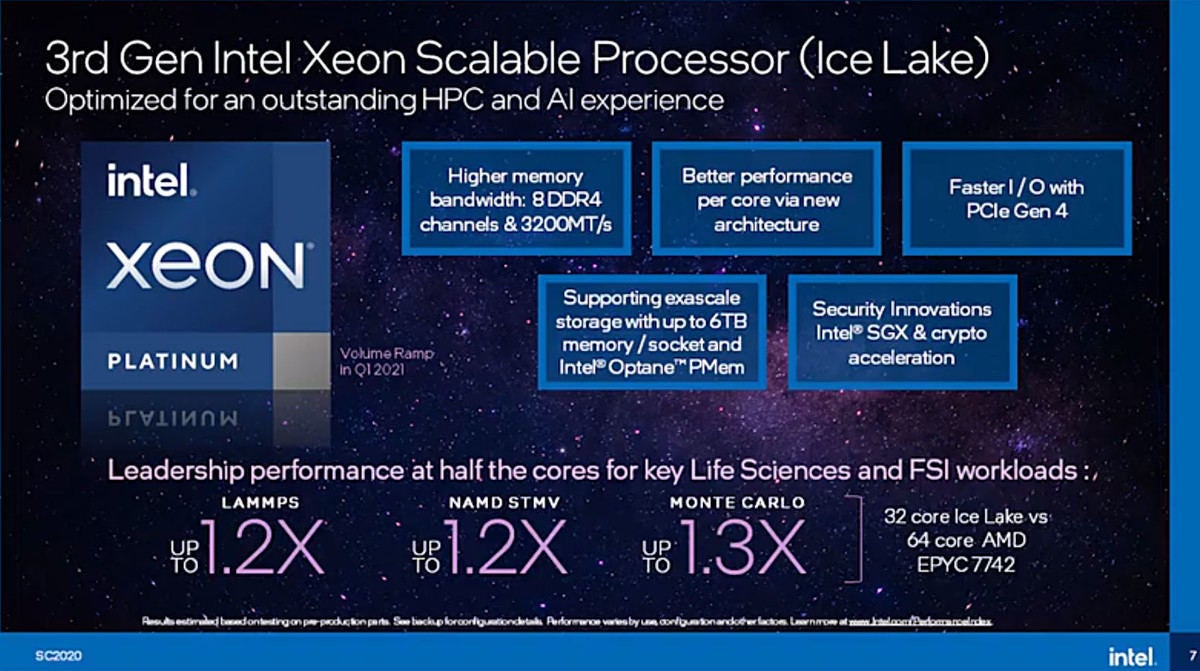

そのIce Lake-SP、内部構造などは2020年8月のHotChipsで公開された(のだが、Ice Lake-SPに関しては安藤先生の分担で、まだ記事が上がっていない)が、その性能の一端が2020年11月のSC20で紹介された(Photo04)。コア数はEPYC 7742の方が倍なのに、性能はIce Lake-SPがLAMMPSで1.2倍、NAMD STMVでも1.2倍、Monte Carloで1.3倍とされている。もっともこれ、どれもAVX-512にフルに最適化されたベンチマークばかり、という問題もあるので、この数字をそのまま鵜呑みにはしにくい。

-

Photo04: 対象は64 CoreのEPYC 7742×2のシステムで、これを32 Core IceLake-SP×2のシステムと比較したそうだ。Ice Lake-SPの方は動作周波数2.2GHzで、メモリはどちらも256GB DDR4-3200だそうである。

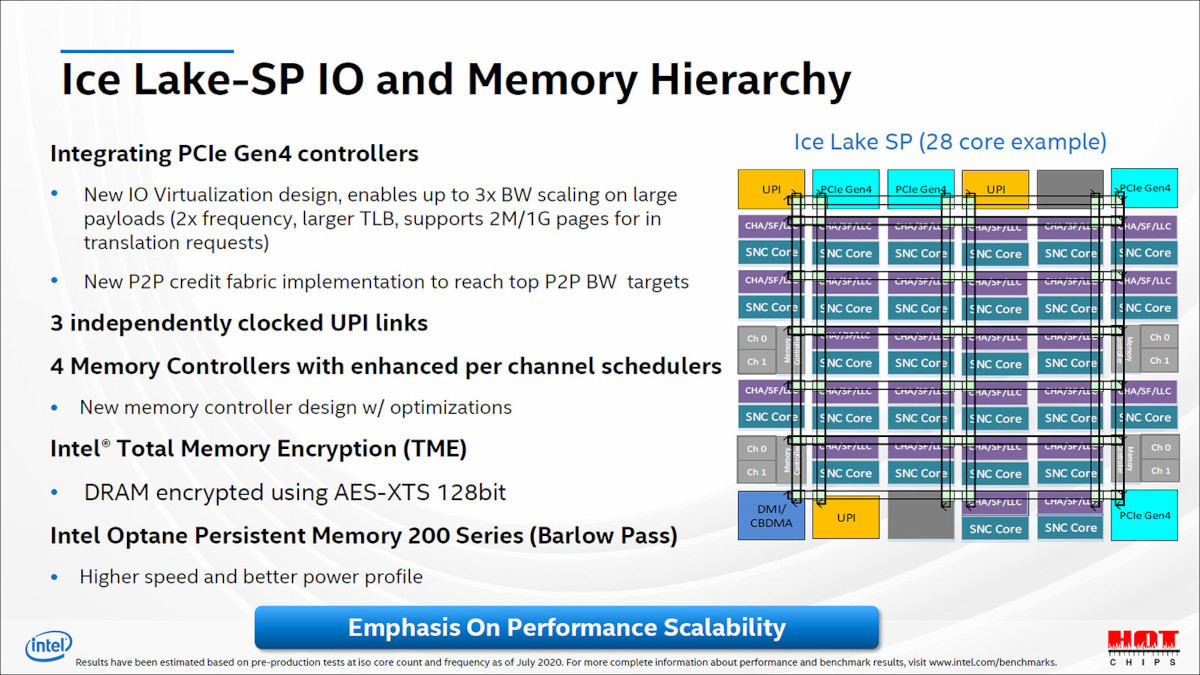

ちなみにHot Chipsでは28 Coreの構成が紹介されたが、先ほどのベンチは32 Coreのものだそうで、つまりHotChipsで紹介されたものがMCC(Mid Core Count)で、この上にHCC(High Core Count)のものがラインナップされているということになる。28コアの場合、ラフに言って7×6のタイル状にユニットが配されており、このうちMemory×4、UPI×3、DMI/CBDMA×1、PCIe Gen4×4の12ユニットがCPUコア以外に利用されているので、最大でも30 Coreが限界であり、ここから2つユニットを無効にした(Yield対策の可能性もあるが)結果が28 Coreとなる(Photo05)。これがMCCだとすれば、例えばHCCは8×6で48ユニット分のスペースを持ち、うち12がCPU以外に使われて最大36 Coreという計算になる。実は36 CoreのIce Lake-SPの結果がGeekBenchに登録された、なんて話もあるのでこの数字は割と整合性が高い。

ただMCCとHCCの差がそんなに小さくていいのか? という疑問も無くはない。実はIntelは2019年8月に、1ソケットで56 Coreの製品の投入を予告していた(このあたりの話はここで書いた)。もしこれをIce Lake-SP世代で実現するつもりだったとすると、HCCは8×9の72ユニットで、ここから12ユニット抜いて60ユニット。冗長部を4ユニットほど設けて56Core、という可能性もありそうな気がする(ここまでやってもEPYCの64 Coreには追い付かないのだが)。なおこれをCore-X向けに転用する、という話は今のところ聞こえてきていない。Ryzen Threadripperの対抗馬という位置づけになるが、もうそれはXeonブランドで良いと割り切ったのかもしれない。

このXeon向けのラインナップがCooper LakeとIce Lake-SPの2つに分かれた状況は、次のSapphire Rapidsで統合される予定で、スケジュール的には一応2021年中に投入されることになる。ただこちらはPCIe Gen5やDDR5をサポート、という時点でパッケージが従来のものと全く互換性がない。実はIce Lake-SPもDDR4を8ch出す時点で既存のXeonと互換性が全くないため、もしSapphire Rapidsが本当に2021年中に登場するとなると、1年の間に2回もプラットフォーム変更が発生することになる。それもあってIce Lake-SPはスキップして直接Sapphire Rapidsに移行する、なんてアイディアを考慮していたベンダーもあったようだが、そのSapphire Rapidsが本当に2021年中に出るとは限らない、という話はここ数年のIntelの遅れを見ると否定しがたいものもあり、それもあって色々苦悩しているようだ。

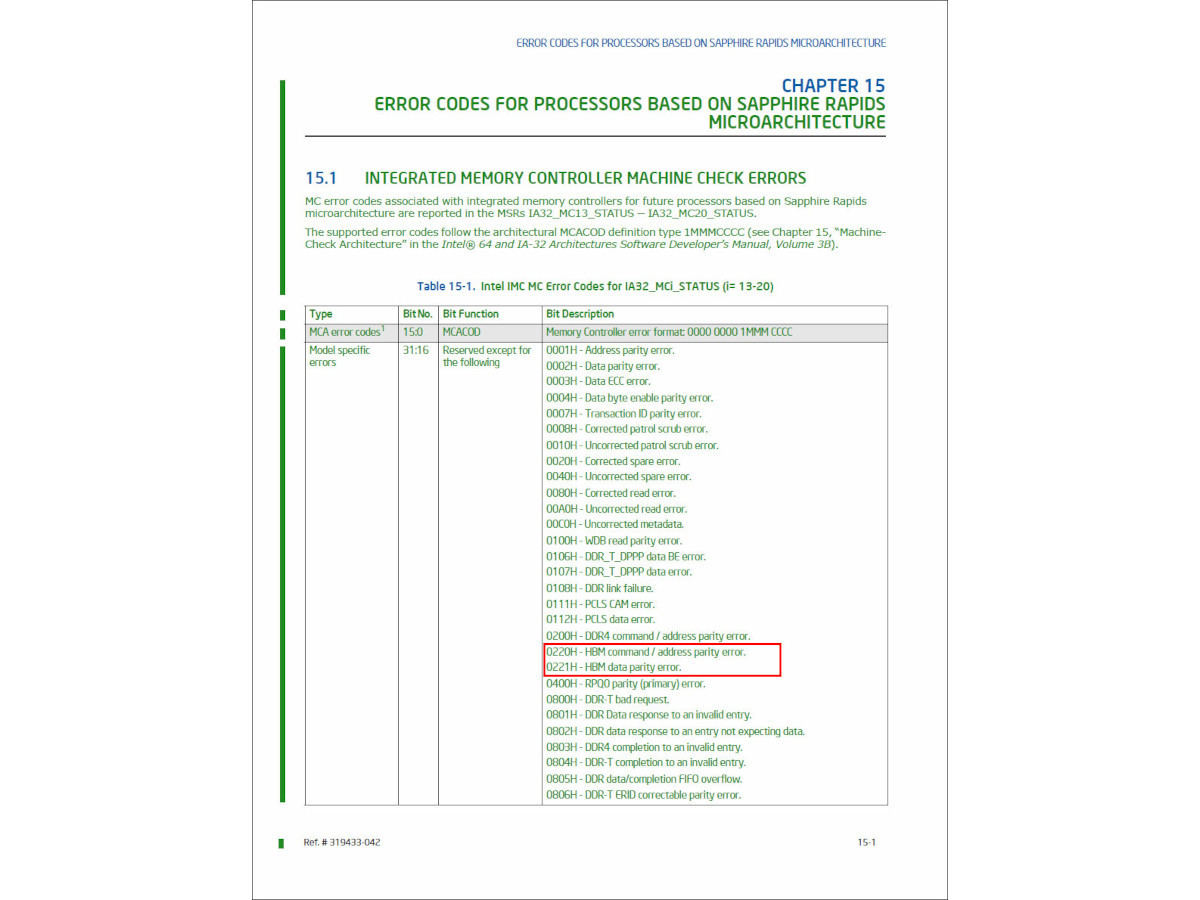

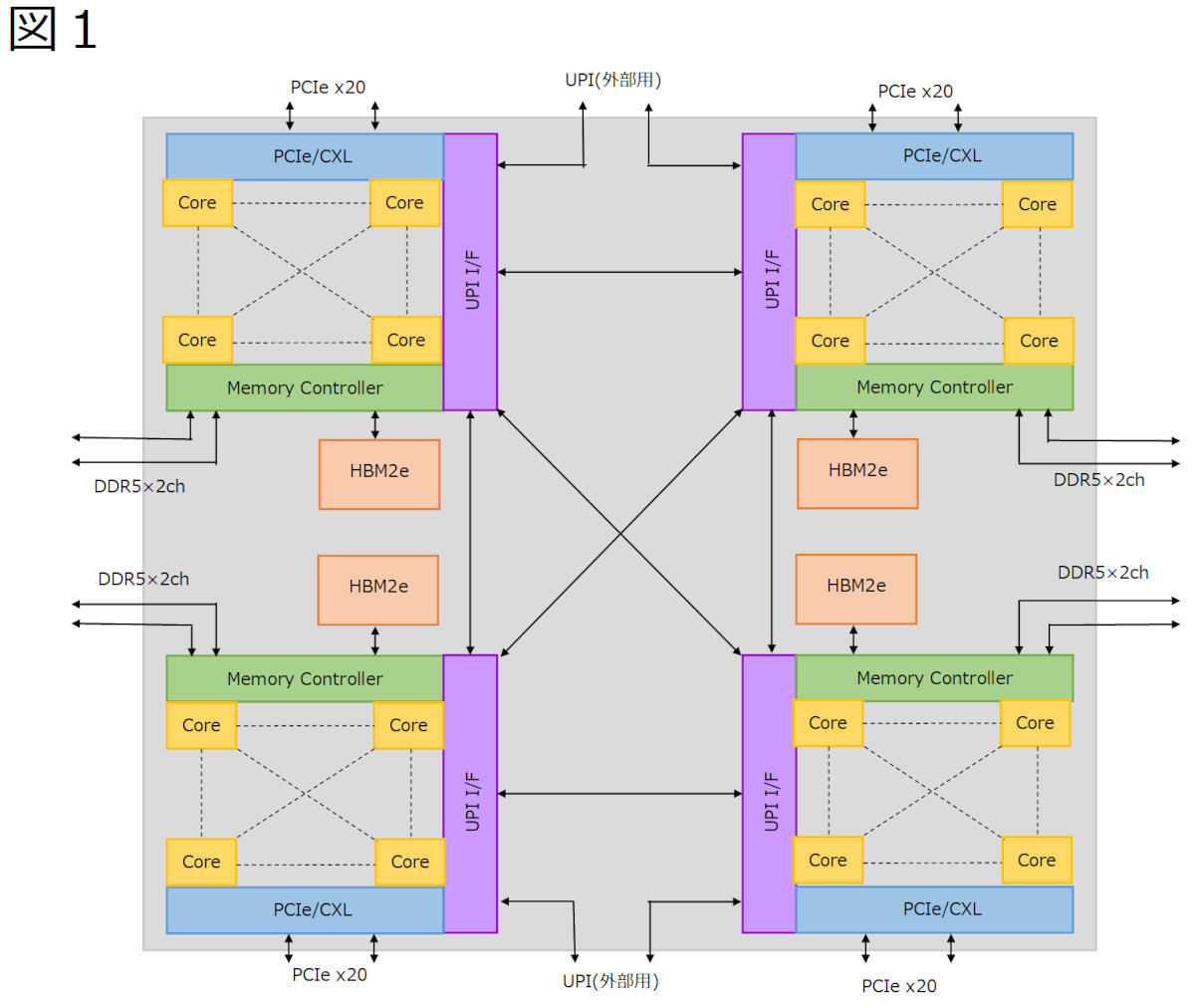

このSapphire RapidsはおそらくGolden Coveコアベースになるのだが、Intelもついにこの世代ではMCM(Multi Chip Module)採用に踏み切る「らしい」。おまけに全SKUではないが、特にHPC向けにHBM2をローカルキャッシュ的に保持するSKUもある「らしい」。このHBM2に関しては傍証がある。2020年12月にIntelは"Intel Architecture Instruction Set Extensions and Future Features Programming Reference"の第42版をリリースしたが、ここにはLAM(Linear Address Masking)という新しい機能、及びSapphire Rapidsで追加された新しいMachine Check Error Codeが記載されている。このSapphire RapidsのIMC(Integrated Memory Controller)のエラーコードには、HBM command/address parity errorとかHBM data parity errorが追加されており(Photo06)、Sapphire RapidsのメモリコントローラにはHBM2のハンドリングが追加されている事が判る。LAMは何かというと、メモリのある特定領域を「仮想記憶に変換しない」という指定を行うためのものだ。要するにHBM2を通常の仮想アドレスにマッピングせずに、巨大なScratchPad的に利用する(ので、ここにアクセスする場合は物理アドレスを指定することになる)場合に利用するもののと思われる。

するとSapphire Rapidsはどういう構造になるのか? というと、図1の様な化け物になる可能性もある。HBM2はオプションだろうし、全部が4ダイというわけではなく、1ダイのみのものや2ダイのものもあるだろうが。