RightMark Memory Analyzer 3.8その4「I-Cache Associativity」(グラフ84~101)

cpu.rightmark.org

http://cpu.rightmark.org/

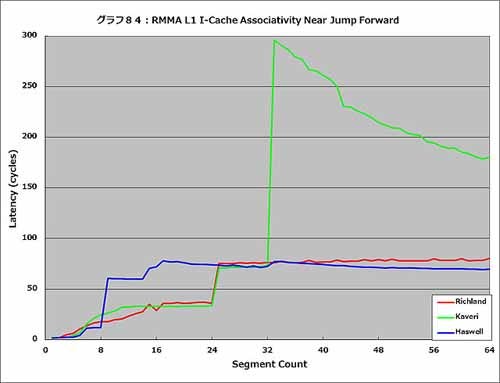

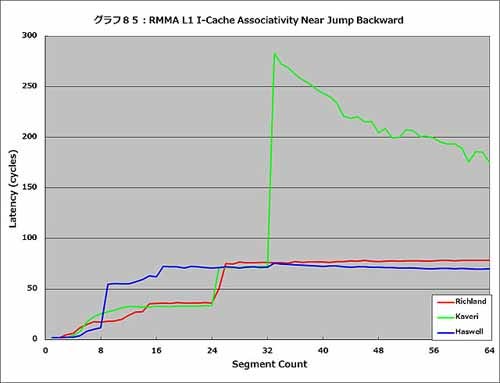

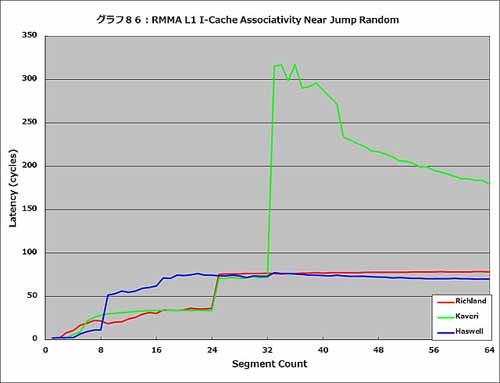

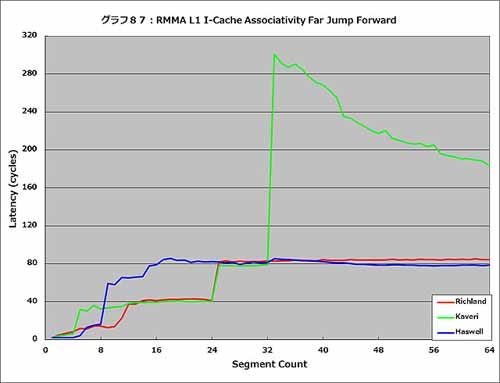

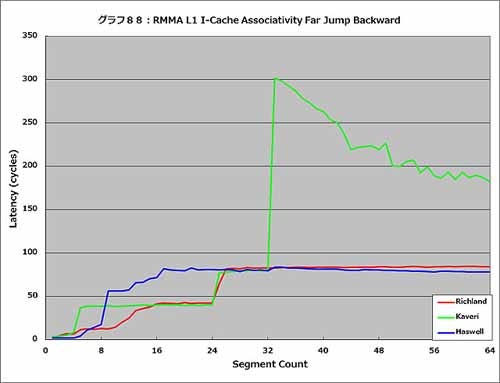

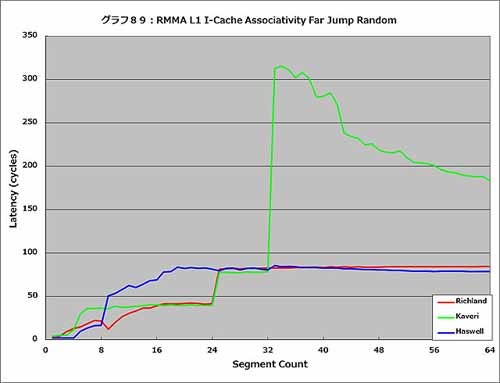

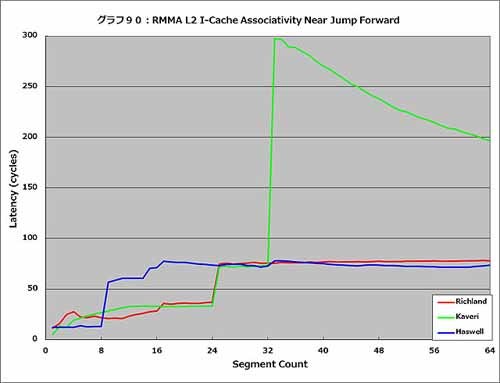

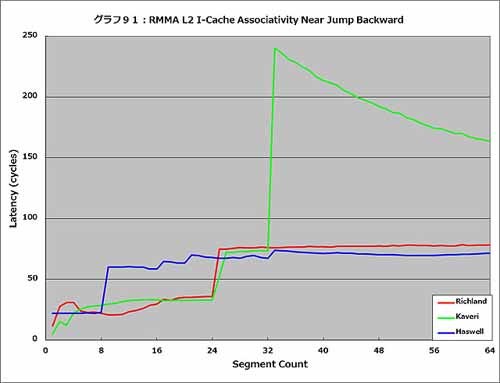

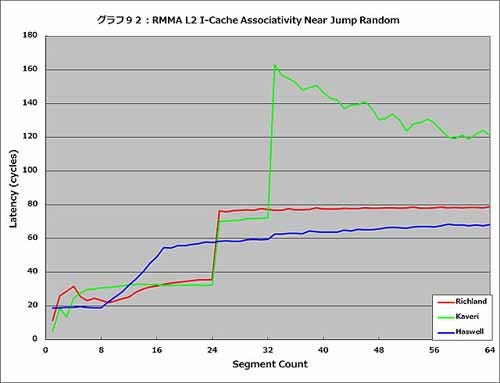

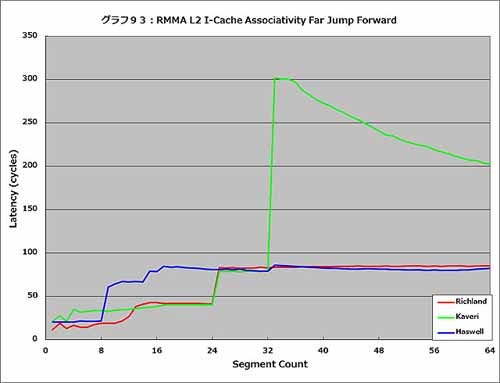

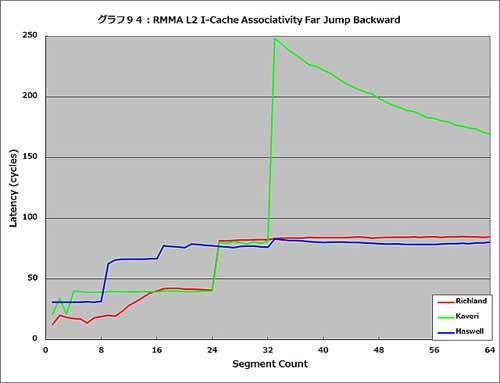

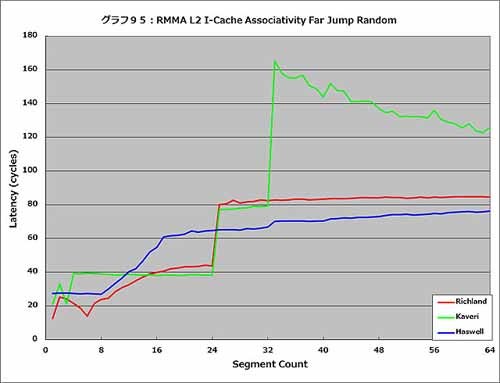

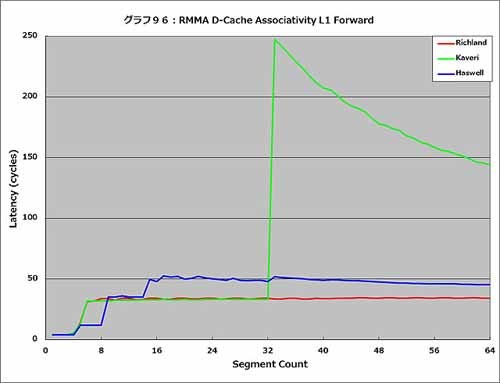

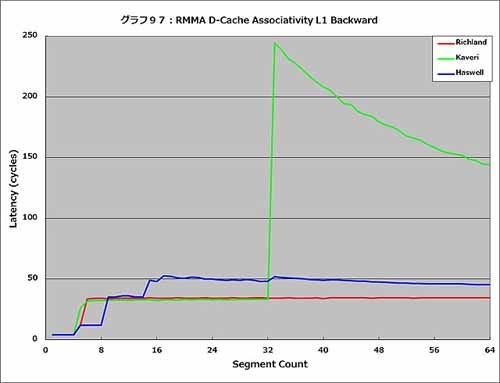

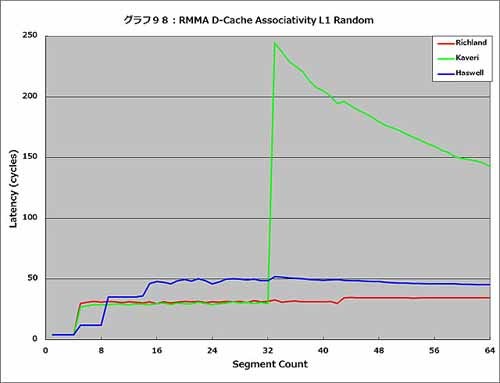

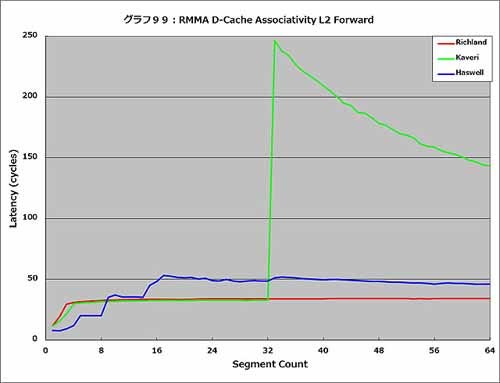

Bandwidth/Latencyを見たついでに、Associativityについても確認しておく。グラフ84~95がI-Cacheである。L1/L2について、それぞれNear/Far JumpでForward/Backward/Randomということで都合12パターンとなる。

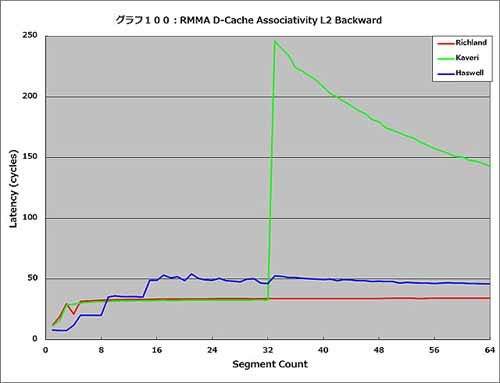

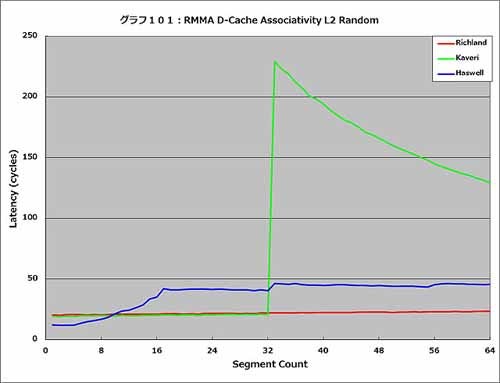

一見して分かるのが、どのケースでもKaveriが何か妙なグラフになっていること。32 SegmentまではRichlandと大きくは差が無いのだが、これを超えてアクセスすると極端にLatencyが増えるのは何かCacheの実装方法が大きく変わった印象を受ける。

最初はこれは3-wayというあまり類を見ない構造のためかと思ったが、後述するように4-wayのL1 D-Cacheでも16-wayのL2 Cacheでも同じ構図になっているので、これはキャッシュコントローラ内部のインプリメントの問題ではないかと思う。

この現象はL1 I-Cache(グラフ84~89)だけでなく、L2 I-Cache(グラフ90~95)でも全く同じだし、続いて行ったL1 D-Cache(グラフ96~98)、L2 D-Cache(グラフ99~101)も全く同じ傾向で、とにかく性能を上げるためには32segmentを超えない範囲でアクセスするような最適化が必要ということになる。これはちょっと意外な制限であった。