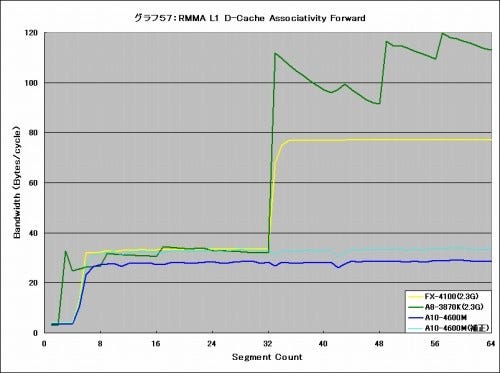

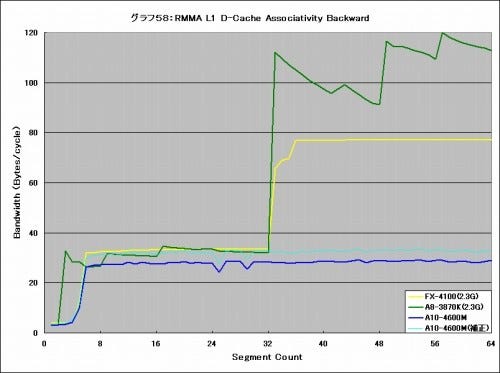

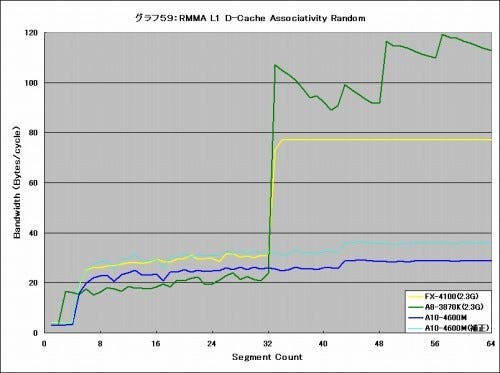

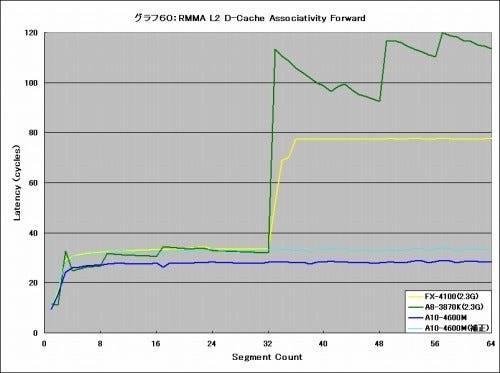

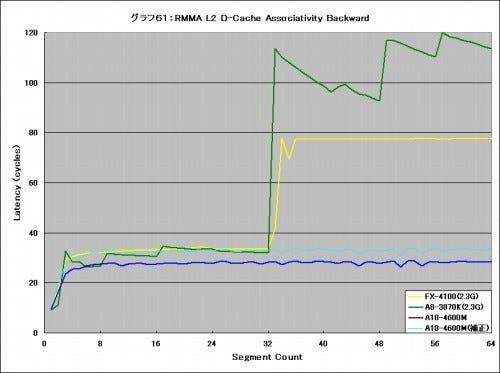

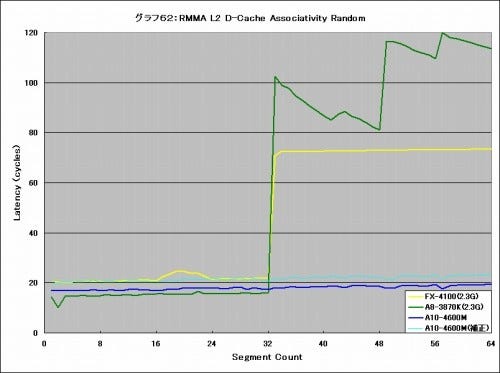

■ D-Cache Associativity(グラフ57~62)

D-CacheのLatencyについてもう少し調べてみた。グラフ57~62はL1/L2におけるAssociativityを測定したものだ。元々L1/L2のAssociativityそのものはPhoto62に示すように4way(I-L1)/2way(D-L1)/16wayとなっているが、ではそのway数を超えて連続にアクセスが来たらどうLatencyが増えるか、を測定するのがここでの目的である。結果はちょっと面白いものになった。どのパターンでも、32segmentまでは一定のLatencyでアクセスできる。A10-4600Mの結果は殆ど暴れていないが、一応補正値の方を基準に考えれば、まぁ同等といったところ。ところが32segmentを超えると、A8-3870Kは大幅に数字が暴れるし、FX-4100は安定しているもののLatencyが倍増するのに対し、A10-4600Mはほぼ一定に保たれている。このあたりはキャッシュアクセスのメカニズムを少し変更したのかもしれない。