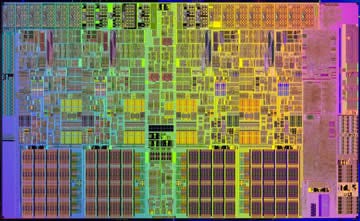

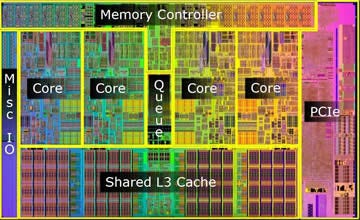

ちなみに今回の発売に合わせ、IntelからはLynnfieldのダイ写真(Photo03)や内部ブロック図(Photo04)が公開されている。

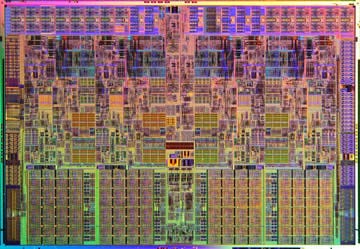

以前のNehalemコアのダイ写真(Photo05)やNehalemのブロック図(Photo06)と比較すると、Lynnfieldは、

- コアの構造はNehalemとほぼ同一に見える

- メモリコントローラもそれほど変更があるように見えない。少なくとも3ch→2chに減じたという様子はここから伺えない

- コアの左端下側、NehalemのQPI 0にあたる部分は完全にDead(無駄)にしている。が、右側のブロック、MISC IOとQPI 1のブロックは、実際にはPCIeとして説明されている部分の右端に存在しているように見える。つまりCore/L3 CacheとMISC IO/QPI 1の間にPCIeのコントローラをはめ込んだ構造に見える

といった特徴を持つ。ここから判ることは、

- LynnfieldはNehalemとは全く別コア。

- 今後、LynnfieldにQPIを追加した派生型が簡単に作れそう。というか、Jasper ForestがLynnfieldをベースにQPIとESIを追加したものになるだろう。

というあたりだろうか。筆者は以前この記事で、Nehalem/Nehalem-EPとLynnfield、Jasper Forestが全て同じダイを使っている、という前提のもとに構造を解説したわけだが、これが見事に外れた事になる。

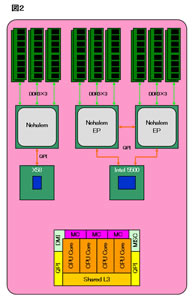

ではどんな構造になっているか、を改めて考え直したのが図2~4である。まず図2はNehalem/Nehalem-EP向けのもので、これは説明の必要はないだろう。次に図3のLynnfieldだが、これはPCIeのコントローラを追加した形になる。右下にQPIのI/Fが残っている訳だが、上で述べた理由以外にももう一つ引っかかるものがあり(これは後述)、とりあえず(使っているかどうかはともかく)残っていると考えている。で、このLynnfieldをベースにしたのが図4のJasper Forestという訳だ。実際のところ、ESIとDMIで回路を共通に出来れば、ひょっとするとJasper ForestとLynnfieldは同じコアかもしれないが、駄目だと3種類ものコアが45nm世代で入り混じることになる。如何に開発費をケチらないIntelとはいえ、ここまで贅沢なコアの使い分けをするとは正直考えていなかっただけに驚きである。

もう一つ言えば、なんでこんなにPCIeのコントローラのダイサイズが大型化するのか、も疑問が残る部分だ。90nm世代ならばともかく、45nm世代の現在でここまでダイサイズを占有するとなると、ひょっとしてPCIe Rev 2.1の拡張仕様を全面的に取り込んだのかもしれない。