2023年6月に京都で開催される「2023 Symposium on Technology and Circuits」の主催者が回路設計分野の注目論文を紹介している。その中で、今回はアナログ回路関連の注目論文を紹介するほか、デバイス・プロセス技術および回路設計分野のワークショップについても紹介したい。

アナログ回路設計:入力インピーダンスの高い高性能離散時間増幅器をスイス工科大が開発

- An Energy-Efficient Impedance-Boosted Discrete-Time Amplifier Achieving 0.34 Noise Efficiency Factor and 389 MΩ Input Impedance (論文番号:C19-2)

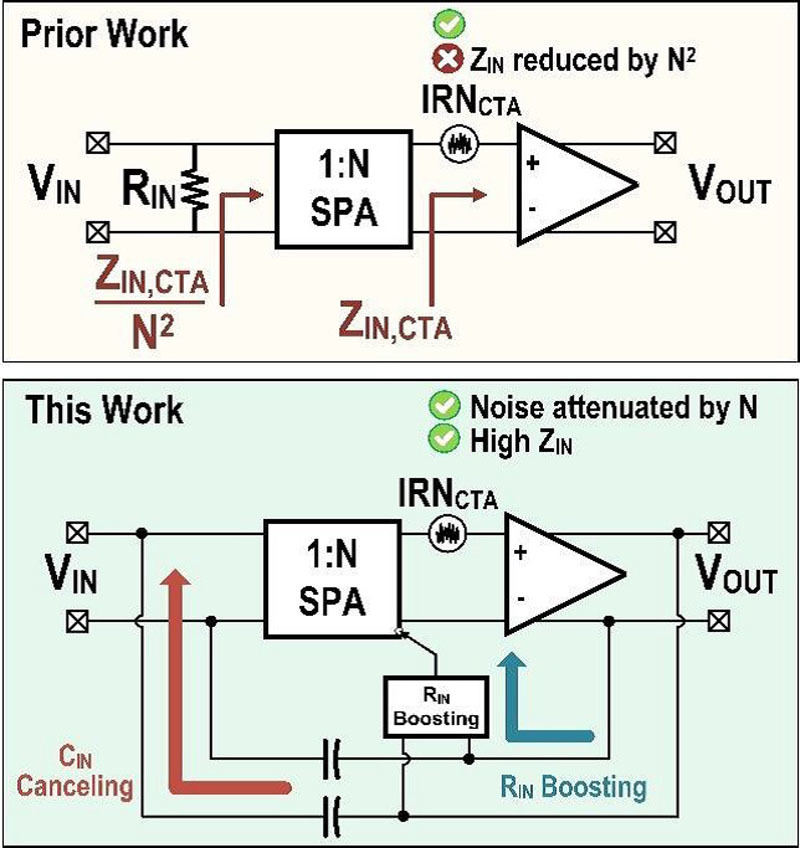

限られた消費電力でノイズの少ない増幅を行うことが、超低電力センサノードでは求められる。従来の直列-並列変換器ベースのアンプは低ノイズであったが、入力インピーダンスが低いという課題に直面していた。

今回、スイス連邦工科大学チューリッヒ校(スイス工科大)の研究グループは低電力センサシステム向けにノイズ効率の良いアナログフロントエンドを報告する予定。提案されるアナログフロントエンドは、入力抵抗ブーストループと容量性正帰還ループを用いて入力インピーダンスを389MΩまで引き上げた直列並列変換器ベースの低ノイズアンプを採用している。このインピーダンスブースト技術により、先行研究と比べて入力インピーダンスを39倍も改善したという。また、このアナログフロントエンドは370nWの低電力でありながら、これまで報告された研究の中で最も低いノイズ効率係数0.34と電力効率係数0.1をそれぞれ達成したとも主張している。

ADC設計:小型高性能A/Dコンバータをミシガン大学が開発

- A 0.024mm2 84.2dB-SNDR 1MHz-BW 3rd-Order VCO-Based CTDSM with NS-SAR Quantizer (NSQ VCO CTDSM) (論文番号:C4-2)

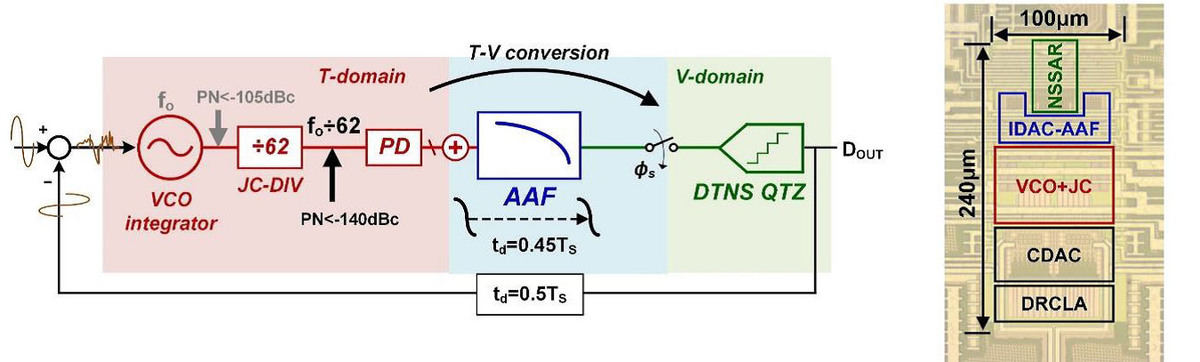

電圧制御発振器(VCO)型積分器はその小面積性、プロセススケーラビリティ、非飽和積分範囲、固有のミスマッチパターンニングが連続時間型ΔΣA/Dコンバータ(ADC)に適していたが、達成できる分解能と帯域の間にトレードオフがあった。

今回、ミシガン大学などの研究チームはノイズシェイピング型SAR量子化器を用いたVCOベースの連続時間型ΔΣ変調器を提案する予定。アンチエイリアシングフィルタを介することでVCO型初段から出力される時間領域情報を直接電圧領域の情報としてノイズシェイピング型SAR量子化器でサンプルすることを可能としている。28nm CMOSによるプロトタイプはサンプリング速度100MS/s、消費電力1.62mWで動作し、1MHzの帯域においてSNDR 84.2dB、ダイナミックレンジ86.8dBを達成している。

なお、VLSIシンポジウム2023では、人工知能、機械学習、IoT、ウェアラブル/埋め込み型生体医療アプリケーション、ビッグデータ、クラウド/エッジコンピューティング、仮想現実(VR)/拡張現実(AR)など、先進のVLSI技術開発、革新的な回路設計およびそれらを実現するアプリケーションを取り上げており、今後のVLSIの進む方向を把握する絶好の場になっている。

初日に6件のワークショップが開催、ナノエレクトロニクス国際会議も併催

論文発表のほか、VLSIシンポジウムでは、初日に6つのワークショップが開催される。本会議では議論されることが少ないが重要な分野について議論されることになっており、主催者側は、参加者が自分の専門外のさまざまな分野の造詣を深める機会を提供することを目的としているようである。

プロセス・デバイス技術分野のワークショップとしては、以下の3件が開催される。

- EUV lithography & path to high NA EUV patterning solutions(EUVリソグラフィと高NA EUVパターニングソリューションへの道筋)

- Towards Functional Backside: What's next after Backside Power Delivery?(裏面の機能化に向けて - バックサイド電源配線の次は?

- The Deployment of Materials to System Co-Optimization Methodology (MSCO) to Enable Rapid PPACt Assessment for Advanced Node Technology Development(材料からシステムまでの最適化先端ノード技術開発のPPACtアセスメント)

また、回路設計分野のワークショップとしては、以下の3件が開催される。

- Uniform and Rigorous Benchmarking of Machine Learning ICs and Systems(機械学習ICとシステムのベンチマーク)

- 3D image sensor(3次元イメージセンサ)

- Open Source PDKs and EDAs, community experiences toward democratization of chip design(オープンチップ設計へのオープンソースPDK/EDAの有効活用)

このほか、京都開催のVLSIシンポジウムとしては、4年ぶりにデモセッションが復活する。技術と回路の両セッションから厳選された論文著者による講演内容の実演がおこなわれ、デバイス特性、チップ動作、およびそれらのアプリケーションを通して、著者と対話できる。

また、VLSIシンポジウム併催の独立イベントとして、6月11日ならびに12日にかけて「Silicon Nanoelectronics Workshop 2023(SNW2023)」が、応用物理学会と米IEEE Electron Device Societyの主催でVLSIシンポジウムと同じ会場で開催される。ナノエレクトロ二クスとVLSIのギャップを埋めることを目的としているという。