VLSIシンポジウム 2022では、メモリに関するさまざまな発表が行われる。今回は、そんな発表の中からプログラム委員会がイチオシする注目論文を7件紹介したい。

メモリ関連の注目論文

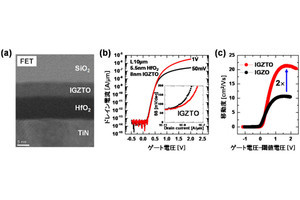

2-1:垂直CAA型のIGZO FETを用いた3D-DRAM技術(Huawei)

Huaweiが中国科学院マイクロエレクトロニクス研究所とともに垂直Channel-All-Around(CAA)型のIGZO(In、Ga、Zn、Oにより構成された透明な酸化物)-FETを用いた3次元DRAM技術を報告する予定。

実効デバイス面積は50×50nm2以下、IGZO厚3nm、HfOx絶縁膜を用いたIGZO-FETは、32.8μA/μm(Vth+1V)でサブスレッショルド特性92mV/decを示したとする。優れた温度安定性と信頼性を有し、PBTS(正ゲートバイアス温度負荷)特性は-40℃から120℃の範囲で確認されたという。

なお、IGZOは2004年に東京工業大学の細野教授らが、TFT(薄膜トランジスタ)を製作し、Nature誌に発表したことで知られる酸化物である。

米国政府から半導体技術禁輸規制を受けている中国勢がこんな最先端半導体研究まで手掛けており、採択率3割の国際会議で採択されたのには驚かされる。

2-1:ダブルスピントルク磁気接合を用いたMRAM(IBM)

IBMが、ダブルスピントルク磁気トンネル接合(DSMTJs)を用いたサブナノ秒スイッチングで、信頼性と動作速度の両立を実証した。250ps以下の書き込み動作で低いエラー率を達成し、-40℃~85℃の広い温度範囲でタイトな特性分布を実現した。1×1010回の書き込みサイクル後の劣化はないという。DS-MTJは、SOT-MRAMと比較して、動作電流密度が1/10に、パワーは1/3~1/10にまで減少させることができると主張している。

2-3:GST(Ge2Sb2Te5)ベース超格子相変化メモリ(スタンフォード大学)

米スタンフォード大学は、リセット電流および抵抗ドリフト係数の低減を可能にするGST超格子ヘテロ構造を搭載した、先進的な相変化メモリ構造を開発したことを報告する。

X線回折法(XRD)および高角散乱環状暗視野走査透過顕微鏡法(HAADF-STEM)による解析から、超格子構造を有するPCMのリセット電流および抵抗ドリフト係数は、超格子の積層数が増えるほど低減することを見出した。リセット電流~3mA/cm2、7抵抗値状態、抵抗ドリフト係数(~0.002)を実証した。

2-4:オンダイエラー制御方式でRAS機能を強化した16GB 1024GB/s HBM3 DRAM(Samsung Electronics)

HBM(High Bandwidth Memory)は、高い帯域幅、低消費電力、大容量という特徴を持つため、最も好まれるメモリであるが、自動車、データセンター、AIなどの産業用途で使用するには、システムの信頼性、可用性、保守性(RAS)に関する課題を克服しなければならない。

Samsungは、16ビットのワードエラーと2つのシングルビットエラーを同時に訂正できる新しいオンダイエラーコード訂正(ECC)方式を採用した“High Bandwidth Memory-3”(HBM3)DRAMについて報告する予定である。エラー訂正性能を向上させることで、メモリキューブあたりの合計メモリバンド幅1024GB/sを達成し、16GBのDRAMモジュールで実証したという。

2-5:4nm CMOSによる高効率・広帯域6T SRAM設計(Intel)

高スループットのアプリケーションに対して計算処理の電力効率を高めるためには、オンチップメモリの大容量化と高帯域化が課題となっている。従来、6トランジスタによるSRAM(6T SRAM)は低面積要件に対応し、8トランジスタによるSRAM(8T SRAM)はより低い動的電力に対応しているが、それらの両立は困難だった。

Intelは4nmクラスのCMOSテクノロジによる電力効率の高いSRAMを報告する。0.03μm2のビットセル面積で最適化された6T SRAM設計は、8T SRAMと同等の電力と、従来6T SRAM設計に対して5.8倍の動的電力削減を達成したとする。

2-6:ARアプリ向けに連続アクセスパターンを用いてアクセス電力を58%低減した7nm SRAM(Meta)

ARアプリでは、エッジインテリジェンスを可能とするセンサ向けに超低消費電力であることが求められている。従来のSRAMマクロはランダムデータトラフィックに最適化されているため、シーケンシャルデータアクセスを電力削減に有効活用できていなかった。

メタバースを推進するMeta(旧Facebook)は、メモリ設計を計測モダリティ向けに最適化し、メモリへのランダムアクセスするのではなく連続アクセスに特化する方式を提案する。連続したメモリからの読み出し、書き込み動作において、回路動作の回数を最小化しています。この方式により、従来の設計と比較して、読み出し電力を52%、書き込み電力を58%削減したという。Metaがこのようなメモリまで自社で独自開発しているのには驚かされる。

2-7:パルス幅変調入力を用いたAD変換器フリーの抵抗変化型メモリ搭載Compute-in-Memory(CIM)マクロ(ジョージア工科大学)

これまでのCIMマクロでは、積和演算結果をAD変換器でバイナリビットに変換後、各メモリアレイでの演算を実現していた。しかし、AD変換器を含むバイナリビットに変換する回路のオーバヘッドは大きく、AD変換器の量子化誤差による演算精度の低下と言った課題があった。

ジョージア工科大学(GIT)は、メモリアレイ入力にパルス幅変調を適用することでAD変換器を不要にした。積和演算結果をデジタル化するオーバヘッドを省くことで演算に関する回路面積を50%削減し、AD変換器を用いた抵抗変化型メモリ搭載CIMマクロに比べ、11.6倍の電力効率改善と4.3倍の演算効率改善を達成したという。