VLSIシンポジウム 2022では、超微細CMOS技術分野でIntel、imec、TSMC、IBMといったプロセスの微細化の先頭を走る企業群から、その取り組みについての発表が行われる予定である。

微細CMOS技術/回路技術分野

1-1:ハイパフォーマンスコンピューティング向けにEUV露光を用いた4nmトランジスタ技術「Intel4」(Intel)

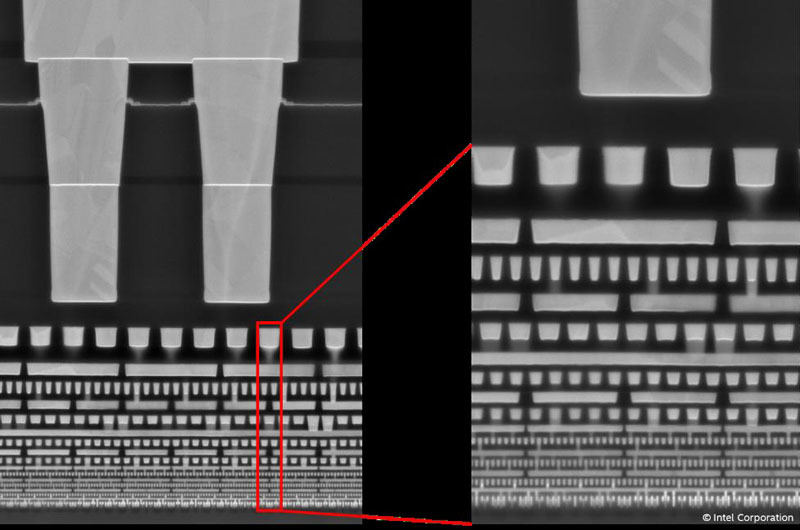

Intelの4nmプロセスである「Intel 4」は前世代の「Intel 7」に比べて集積度が2倍向上し、性能は20%改善、デザインルールは、ゲートピッチ50nm、フィンピッチ30nm、最小メタルピッチ30nmとなるとしている(図1)。

トランジスタは8つのVTオプション(NMOS 4VT/PMOS 4VT)を提供しており、設計者が消費電力と性能の要求から最適なVTオプションを選択することが可能になっている。

Intel 4ではEUV露光技術を、プロセス最適化と歩留改善のために広範囲に適用。クリティカル配線は16層で、Cu配線を改良し、エレクトロマイグレーション改善と配線抵抗の低抵抗化を実現しているとする(図2)。

1-2:埋め込み電源配線(BPR)を介したウェハ両面配線を持つ微細FinFETプロセス(imec)

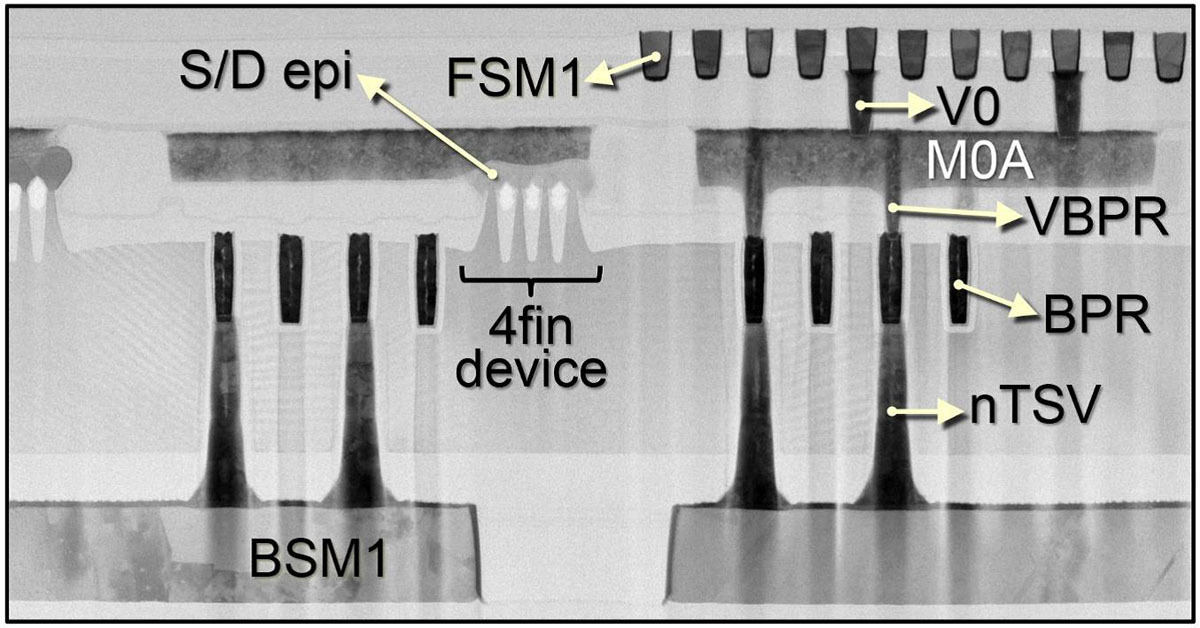

ベルギーのimecは、トランジスタの下に電源配線を埋め込むBuried Power Rail(BPR)技術を報告する(図3)。

信号配線と電源配線で配線配置の競合が発生しなくなるため、IRドロップが低くなり配線密度が高くなる。ウェハの両面からの、BPRを介した電源接続を可能にする新しい配線方式を有する、先端FinFETプロセスについて報告する予定だという。

1-3:ウェハスケール半自動転写プロセスを用いた高性能WS2トランジスタ(TSMC)

TSMCは、半金属Biと2次元半導体WS2間の弱結合界面を利用した、単層CVD-WS2用のウェハスケール半自動乾式転写プロセスを用いたトランジスタ技術を報告する予定。

単層2D半導体は、原子スケールのチャネル厚さにおいても良好なキャリア移動度が維持され、短いチャネル長(LCH<10nm)での新チャネル材料として有望だという。新単層転写法は、ウェハスケールで実証されており、n-FET において、135nmのゲート長で最大250μA/μmの高いオン電流を達成したという。

1-4:200+Gb/sシリアルリンク向け72GS/s、8-bit DACベース4nm FinFET CMOS有線送信機(IBM基礎研究所)

データセンターにおけるネットワーク帯域増加の需要から、50GBaudを超える回線ごとのシンボルレートで動作する電力効率の良い電気相互接続の需要が高まっている。しかしながら、SST(ソースシリーズ終端)設計を基礎とした先行研究では56GBaudを超えることはできなかった。

IBM基礎研究所は超高速有線シリアルリンク向け送信機を報告する。72GS/s動作でSSTを用いた8bit DACを基礎手法とし、72GBaudまで押し上げている。4nm FinFET CMOS ICは216Gb/s PAM8と212Gb/s QAM64 OFDM動作を288mWの電力消費で達成したという。

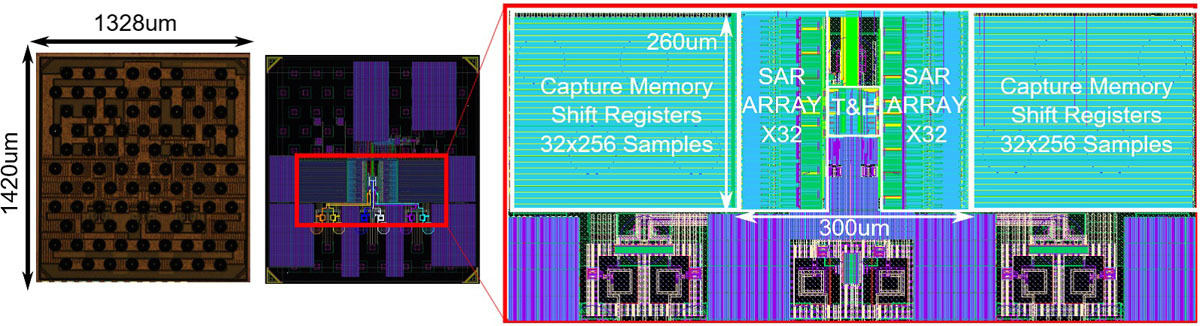

1-5:ブートストラップサンプラとAB級バッファを用いた4nm CMOS 8-bit 56GS/s 64チャンネルタイムインターリーブ型ADC(IBM基礎研究所)

近年のADCベースの高速シリアル通信用レシーバでは112Gb/s超の速度要求に応えるためタイムインターリーブ技術が必須となっている。速度要求を満たすには高いインターリーブ数が必要になるが、サンプル回路性能が制約となっている。

IBM基礎研究所は4nmプロセス技術において0.8Vという低電源電圧で動作可能かつ最大振幅0.8Vppの入力信号まで受付可能である、新たなAB級入力バッファとブートストラップ型トラック・ホールド回路を提案する。IBMのADC回路は27GHz超の帯域を実現しつつ、47fJ/conv.stepという高い電力効率を示したという。