現在、ラストレベル(CPUから見て一番遠くに位置する)キャッシュメモリ・アプリケーションでのスピン軌道トルクMRAM(SOT-MRAM)デバイスの使用には、スケーラビリティ(微細化可能性)、動的消費電力低減(書き込み操作時の大電流の低減)、および製造可能なコンパクトなフィールドフリー・スイッチング ソリューションの必要性といった問題がある。

2022年末に開催されたIEDM(国際エレクトロンデバイスミーティング)にて、imecはこれらの問題を一気に解決する新しいSOT-MRAMアーキテクチャを発表した。

このソリューションの鍵を握るのは、ゲート電圧アシスト動作、マルチピラー構成、外部磁場の除去、およびCMOSと互換性のある製造技術などである。

これらの設計上の改善に加えて、高スイッチング速度(300ps)とデータ書き換え可能回数1012回以上の耐久性により、この新しいデバイスは組み込みメモリアプリケーションにおけるSRAMの魅力的な代替品候補になってきている。

本稿では、2回に分けて、そうした高密度ラストレベル・キャッシュメモリ・アプリケーションへの扉を開く新しいSOT-MRAMアーキテクチャをimecの開発担当者が解説する。

サブnsのスイッチング速度と高耐久性

近年、半導体チップ業界はSOT-MRAM技術の開発にますます関心を寄せている。SOT-MRAMは、高性能コンピューティングやモバイルアプリケーションのL3(およびそれ以上の)キャッシュメモリなど、組み込みメモリアプリケーションに有望な特性を持つ不揮発性メモリである。

現在、この役割は通常、超高速のSRAMによることが多いが、スケーリング上の制約によりSRAMのビット密度を増加するのが難しく、メモリ関係者は代替手段を探す必要に迫られている。さらに、SRAMのビットセルは、メモリがアクティブではないときに消費電力が増加するため、スタンバイ電力の低下が困難である。MRAMなどの不揮発性メモリは、より小さなビットセルを提供する可能性があるだけではなく、不揮発性による待機電力の問題も解決してくれる可能性がある。

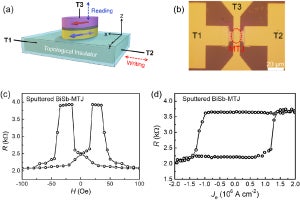

SOT-MRAMは、成熟した技術であるSTT-MRAMから進化したMRAMで、耐久性が高く、2つのバイナリ状態間の切り替えが高速で行えるため、キャッシュへの応用の可能性が高い。STTおよびSOTいずれの種類のMRAMでも、磁気トンネル接合(MTJ)がメモリセルの「心臓部」を構成している。このMTJでは、強磁性固定層(CoFeB)と強磁性自由層(CoFeB)との間に薄い誘電体層(MgO)が挟まれた構造になっている。

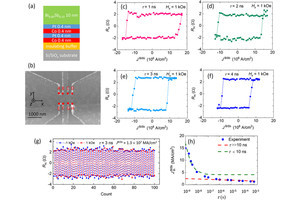

メモリセルの書き込みは、自由層(MRAMビットセルの“ストレージ”層)の磁化を切り替えることによって実行される。読み取りの場合、MTJの磁気抵抗は、接合部に電流を流すことによって測定される。このトンネル磁気抵抗(TMR)は、自由層と固定層の磁化の相対的な向き(つまり、平行(1)または逆平行(0))に応じて、大きくなったり小さくなったりする(図1)。

STT-MRAMとSOT-MRAMの主な違いは、書き込みプロセスに使用される電流注入ジオメトリにある。STT-MRAMでは、電流がMTJに垂直に注入されるが、SOT-MRAMでは、隣接するSOT層(通常はタングステン(W)などの重金属)の面内で電流が注入される。したがって、SOT-MRAMでは、読み取りパスと書き込みパスが分離され、デバイスの耐久性と読み取り安定性が大幅に向上する。面内電流注入は、STT-MRAM動作のスイッチング遅延も回避できる。2018年、imecは優れた耐久性(>5×1010スイッチングサイクル)と300pJの動作電力を備えた、スイッチング速度210psの信頼性の高いSOT-MRAM スイッチングを初めて実証した。

SOT-MRAMの課題:面積消費、高い注入電流、製造可能性

不揮発性であるため、SOT-MRAMは高セル密度のSRAMよりもスタンバイ電力を大幅に低くすることができる。しかし、書き込み操作には大電流が必要なため、動的消費電力は依然として比較的高いままである。

さらに、組み込みメモリアプリケーションでSOT-MRAMをSRAMの真の競争相手にするためには、密度スケーリングの革新が必要である。従来の面内磁化の代わりに固定層と自由層(p-MTJと呼ばれる)に垂直磁化を採用すると、メモリセルを長方形にする必要がなくなるため、スケーリングの可能性が向上する。

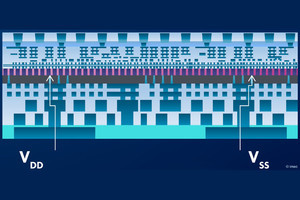

しかし、重要な課題はデバイスアーキテクチャにある。柱状構造のSTT-MRAMは2端子デバイスである。メモリアレイ構成で実装される場合、読み取りまたは書き込み用のメモリ要素を選択するために、MTJセルごとに1つの選択デバイス(通常はアクセストランジスタ)のみが必要である。

個別の読み取りパスと書き込みパスを備えたSOT-MRAMは、3端子デバイスである。この場合、メモリ要素ごとに 2つのアクセストランジスタが必要である。そのため、独立した読み取りパスと書き込みパスは信頼性増加の利点をもたらすが、追加の金属ワイヤに付属する追加のアクセストランジスタが原因で、追加のスペースが必要となってしまう。

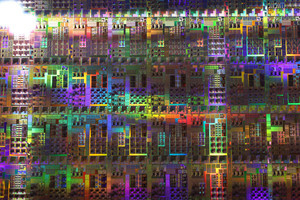

また、製造可能性の課題もある。2018年、imecはCMOS互換プロセスを使用して300mmウェハ上にSOT-MRAMデバイスモジュールを本格的に統合することを実証し、産業への普及を促進した。しかし、SOT-MRAM-p-MTJビットセルの実用的な実装は、書き込み操作中に余分な面内磁場が必要なため、依然として妨げられている。この磁場は、対称性を破り、確定的な磁化スイッチングを確保するために必要である。つまり、この磁場がなければ、書き込み電流を流した後にフリー層がどのような状態になるかを知ることは不可能である。SOT-MRAMの開発段階では、この磁場は外部磁場によって生成される可能性があるが、最終的なデバイスでは、デバイス内で堅牢でコンパクトな磁場生成が必要になる。

(次回に続く)

|

Sebastien Couet

2008年に独ハンブルグ大学で物理学の博士号を取得後、2009年から2014年までベルギーKatholieke Universiteit Leuven(KUL)で博士研究員を務め、磁性/酸化物ヘテロ構造の界面物理を研究。2014年にimecに入社。現在は磁気に関するプログラムディレクターを務めている。組み込みおよびスタンドアロンアプリケーション向けのさまざまなMRAMベースのメモリコンセプトや、その他の探索的磁気デバイスコンセプトの開発を指揮している。 |

|

Gouri Sankar Kar

2002年にインド工科大学で半導体デバイス物理学の博士号を取得後、ノーベル賞受賞者(1985年、量子ホール効果)のクラウス・フォン・クリツィング教授と量子ドットFETについて研究を実施。2006年には、独Infineon/Qimondaにリードインテグレーションエンジニアとして入社。同社にてDRAMアプリケーション用の縦型トランジスタの開発に取り組む。2009年、imecに入社。現在はプログラムディレクターを務めている。スタンドアロンおよび組み込みアプリケーションの両方のSCM、DRAM、およびMRAMプログラムの研究戦略とビジョン立案を担当している。 |