imecの先端パターニング、プロセス、および材料(Advanced Patterning、Process and Materials:APPM)担当のシニアバイスプレジデントであるSteven Scheer氏が、短期的および長期的なパターニングの課題と革新的な解決策を語っている。

それによると、高NA EUVリソグラフィの出現、新しいメモリとロジックデバイスの概念の台頭、およびIC製造の環境への影響を軽減する必要性という状況下で、imecではリソグラフィによるパターニングをどのように推進しているか具体的に解説している。

極端紫外線リソグラフィ(EUVL)は、2019年に先進ロジックファウンドリでの量産に導入されて以降、DRAMメーカーもEUVLの採用を始めている。こうした動きは、ASMLが技術の限界を押し上げる努力を継続してきたからこそ実現できたわけだが、次の進化は高NA(開口数:NA=0.55)のEUVLの導入で、それにより8nmまでのハーフピッチ (ライン&スペースの1/2の寸法:ラインとスペースが同じ寸法ならライン幅を指す)のパターニングを可能にする。

この高NA EUVLの導入サポートに向けimecとASMLは共同でオランダに「High NA EUV Lab」を設立し、高NA EUVLの導入を目指す半導体メーカーの初期開発ニーズへの対応を進めている。また同時に、imecのEUVLパートナー企業たちがHigh NA EUV Labへアクセスすることを可能にし、EUVレジスト、下地層、ドライエッチング、フォトマスク、解像度向上技術(Resolution Enhancement Techniques:RET)および計測技術の準備を進めている。

-

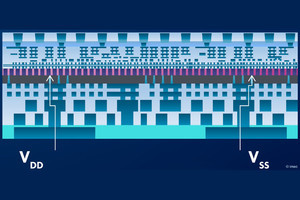

最終的にサブ1nmを目指す微細化のための露光装置技術のロードマップ。(左)既存のEUV露光装置、(右)開発中の高NA EUV露光装置の大きさの比較 (出所:imec Technology Forum Belgium 2022)

高NA EUVの導入における優先事項

最優先事項は、高NAツールがいつ使えるようになるかという点である。ASMLと独Zeissが、すべてのモジュールと光学部品を統合に向けて協業している。低NA EUVの導入の際にも、プロセス関連という側面で多くの画期的なソリューションが開発されてきたが、高NA EUVを効果的に導入するには、さらなる進化が必要である。高NAツールに加えて、EUVフォトレジストの開発は、imecのエコシステムパートナーとの最優先事項の1つである。高NA EUVLの出現により、焦点深度が浅くなり、解像度がさらに向上し、最小加工寸法をさらに縮小できる。もちろん、これは膜厚のダウンスケーリングにもつながり、エッチング中のEUV吸収とパターン転写を最適化するために、新しいレジストと下地層の採用が必要になる。

さらに、数年前に発見された現象であるランダムに発生する確率論的粗さの継続的な改善を進める必要があり、極端な場合には、EUV 露光でパターニングされたレジストの欠陥でさえも改善する必要がある。

歴史的に、フォトレジストのパターニング性能は、解像度、ラインエッジラフネス(Line Edge Roughness:LER)またはローカルCD均一性 (Local Critical Dimension Uniformity:LCDU)、および感度(Resolution・Linewidth Roughness・Sensitivity(RLS)パラメーターとも呼ばれる)によって表される。現在、確率論的に生じる問題の重要性を考えると、プロセスウィンドウを狭めてしまう4番目のパラメータ(ランダム欠陥)をレジスト開発の初期段階から軽減するための研究に取り組んでいる。パートナーと協力して、高NAラボでこれらの新技術を実証する予定である。

形状のサイズとレジストの厚さの両方の縮小は、計測にも影響を与える。マスクパターン転写性能に加えて、劇的な寸法縮小は、潜在的に正確さと精度に影響を及ぼす可能性があることから、計測と検査の性能に悪影響を及ぼす可能性がある。

(次回に続く)

|

Steven Scheer

2019年にAdvanced Patterning,Process and Materials(APPM)担当VPとしてimecに入社した後、2022年にシニアVPに昇進。責任範囲には、パターニング、ユニットプロセスおよびロジック、メモリ、フォトニクス、3D集積の新材料開発が含まれる。それ以前は東京エレクトロン(TEL)でアカウントテクノロジーディレクターを務め、米ポートランドの顧客を担当していた。TELには13年間勤務し、米国や熊本のTELの工場および東京本社R&D部門でパターニングと洗浄のR&Dを担当していた。研究キャリアは、ニューヨーク州フィッシュキルのIBMにて90/65nmのパターニング開発に取り組んだことからスタートした。テキサス大学オースチン校で化学工学分野の博士号を取得 |