測定

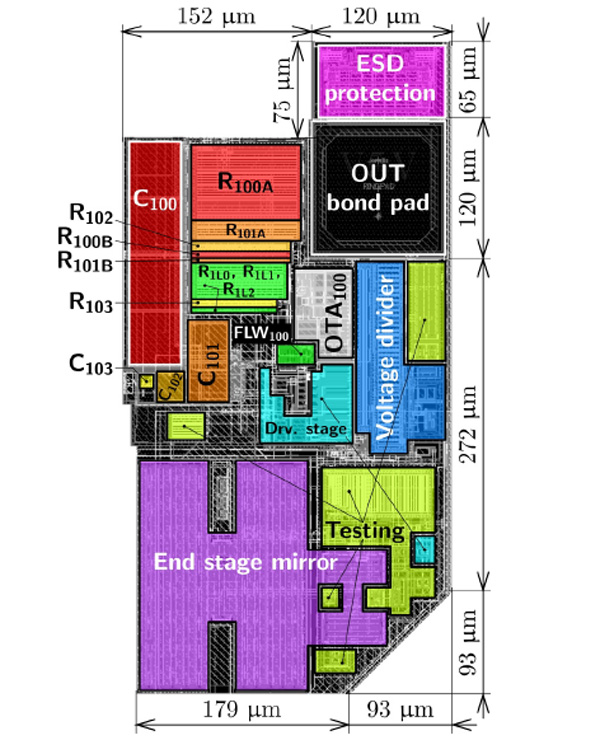

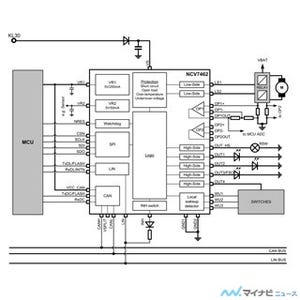

提示LDOは、複合的なミクスド信号の特定用途向けIC内の機能ブロックという形で実現されています。LDOのレイアウトを図17に示します。

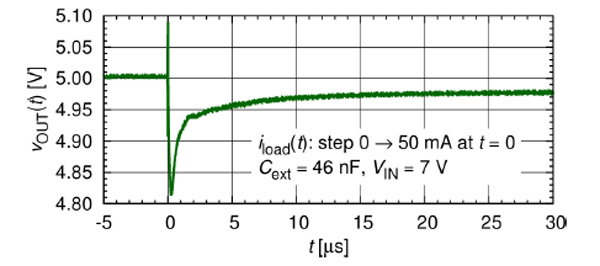

測定は、代表値に近いプロセス・パラメータを持つサンプルを使用し、室温で実施しました。自己発熱を低減すると同時に、LDOの正常動作を確保するために、入力電圧VINを7Vに設定しました。リード端子やボンド・ワイヤでの電圧降下をなくすために、出力電圧(VOUT、vOUT)はボンド・パッド(GND、OUT)で直接測定しました。

LDOの実測DC負荷特性を図18に示します。実測特性は、図14のシミュレーション結果より勾配が大きくなっています。これは内部グランドのシフトによるもので、ボンド・パッドで測定してもこの影響は除去できず、シミュレーションでも考慮されていません。実測した動的出力抵抗は約300mΩです。

負荷電流が0mAから50mAにステップ増加した場合の応答をキャプチャした図19は、電圧降下が200mV未満であることを示しており、大部分は約10μs以内に整定します。50mAから0mAへのステップ減少は図20に示すように、150mV以下のピークを生じ、200μs以内にほぼ整定します。

測定はすべてシミュレーション結果に一致しています。

結論

分数次数制御を採用した低ドロップアウト・レギュレータ(LDO)について説明しました。高精度の電圧レギュレーションと、約300mΩという小さい動的出力抵抗を実現すると同時に、レギュレーション・ループの良好な安定性を維持し、しかも補償ゼロが不要です。任意の大容量外部コンデンサを使用することができ、外部コンデンサに最小ESRの制限は課されません。このLDOは、過酷な車載環境で使用するアナログ回路に対して、高精度の電源電圧を供給することを意図しています。

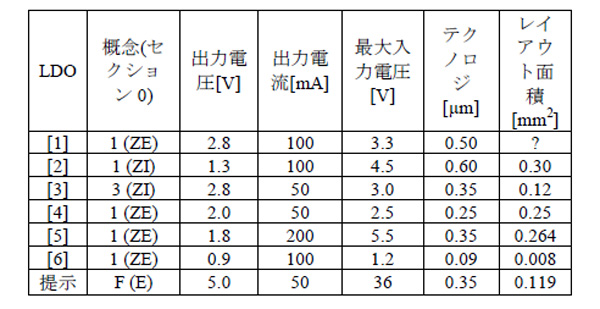

表4に提示LDOと選択した他のLDOの比較を示します。

誤差アンプがアクティブ回路であり、図9に示したR1L0-R1L1-R1L2で構成されるT型回路を使用できるため、非常に大きい抵抗値を使用して左側での抵抗終端を回避できます。今後の作業では、誤差アンプのRCラダーが占有するレイアウト面積をさらに減らすために、分数次数インピーダンスの近似におけるアクティブ素子の高度な利用に集中できます。

参考文献

[1] CHAVA, C.K. – SILVA-MARTINEZ, J. A frequency compensation scheme for LDO voltage regulators. IEEE transactions on circuits and systems I: regular papers, 2004, vol. 51, no. 6, p. 1041–1050. DOI: 10.1109/TCSI.2004.829239.

[2] KA NANG LEUNG, MOK, P.K.T., ASI IT LAU. A low-voltage CMOS low-dropout regulator with enhanced loop response. Proceedings of the 2004 International Symposium on Circuits and Systems, 2004. ISCAS '04, 2014, vol. 1, p. 385–388. DOI: 10.1109/ISCAS.2004.1328212.

[3] MILLIKEN, R.J., SILVA-MARTINEZ, J., SANCHEZ-SINENCIO, E. Full On-Chip CMOS Low-Dropout Voltage Regulator. IEEE Transactions on Circuits and Systems I: Regular Papers, 2007, vol. 54, no. 9, p. 1879–1890. DOI: 10.1109/TCSI.2007.902615.

[4] WONSEOK OH, BAKKALOGLU, B. A CMOS Low-Dropout Regulator With Current-Mode Feedback Buffer Amplifier. IEEE Transactions on Circuits and Systems II: Express Briefs, 2007, vol. 54, no. 10, p. 922 – 926. DOI: 10.1109/TCSII.2007.901621.

[5] AL-SHYOUKH, M., HOI LEE, PEREZ, R., A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator With Buffer Impedance Attenuation. IEEE Journal of Solid-State Circuits, 2007, vol. 42, no. 8, pp. 1732–1742. DOI: 10.1109/JSSC.2007.900281.

[6] HAZUCHA, P., KARNIK, T., BLOECHEL, B.A., PARSONS, C., FINAN, D., BORKAR, S. Area-Efficient Linear Regulator With Ultra-Fast Load Regulation. IEEE Journal of Solid-State Circuits, 2005, vol. 40, no. 4, p. 933 – 940. DOI: 10.1109/JSSC.2004.842831.

[7] MONJE, C.A., CHEN, Y., VINAGRE, B.M., XUE, D., FELIU-BATLEE. Fractional-order Systems and Control – Fundamentals and Applications. 2010, 430 p. ISBN 978-1-84996-334-3. DOI: 10.1007/978-1-84996-335-0.

[8] YANG QUAN CHEN, PETRÁŠ, I., DINGYÜ XUE. Fractional Order Control – A Tutorial. American Control Conference, 2009. ACC '09, 2009, p. 1397–1411. DOI: 10.1109/ACC.2009.5160719.

[9] VALSA, J., DVORAK, P., FRIEDL, M. Network Model of the CPE. Radioengineering, 2011, vol. 20, no. 3, p. 619–626. ISSN 1805-9600.

[10] PETRŽELA, J. Phase Shifters Using Passive Realizations of Fractal Capacitors (Posouvač fáze založené na využití pasivních realizací fraktálních kapacitorů). Slaboproudý obzor, 2014, no. 2, p. 6–12. ISSN 2336-5773.

[11] PETRÁŠ, I. Fractional-Order Feedback Control of A DC Motor. Journal of Electrical Engineering, 2009, vol. 60, no. 3, p. 117–128. ISSN 1335-3632.

著者プロフィール

Pavel Horský (パヴェル・ホルスキー)オン・セミコンダクターの技術スタッフのメンバーで、専門分野はEMC、ESD、信頼性を重視した自動車用アナログ/ミクスド・シグナルIC設計。

1997年から、アルカテル・マイクロエレクトロニクス、AMIセミコンダクター、オン・セミコンダクターで、アナログおよびミクスドシグナル・デザインエンジニア、テクニカル・プロジェクト・リーダー、アナログASIC設計グループのリーダーを歴任。

チェコ共和国ブルノ工科大学で、1994年にラジオエレクトロニクス理学士号、1998年に計測学で博士号を取得。

2011年から同大学准教授として、博士課程の学生向けにアナログデザインコースを担当。60の出版物の著者および共同著者、15の米国特許の起草および共同起草者。

Libor Kadlčík (リボル・カドルーク)

オン・セミコンダクターのチェコ共和国にあるデザインセンターで、アナログASIC設計グループに所属。

チェコ共和国のブルノ工科大学で、2011年に電子通信学の理学士号、また2013年に理学修士号を取得。

現在、同大学の電子通信技術(D-EST)プログラムの博士号を取得中。