自らの工場での半導体製造は手放したものの、半導体の研究開発領域ではimecと双璧をなし、世界最先端の取り組みを今も継続して行っているIBM。そんな同社が2025年12月17日~19日にかけて東京ビッグサイトにて開催されている「SEMICON Japan 2025」にてブース出展し、自社のそうした最新研究の説明などを行っている。

先端プロセスの研究開発に挑んできたIBM

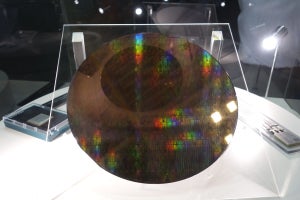

IBMが取り組んできたプロセス微細化技術は現在、Rapidusと提携する形で量産に向けた適用がRapidusの製造拠点「IIM-1」にて進められているが、同ブースでは、その技術のベースとなった2nmプロセスウェハが、半導体トランジスタの構造の変化の流れとともに展示されている。

先端プロセスを手掛ける各社は現在、2nm(2nm相当含む)もしくは3nmプロセスにてGAAトランジスタ構造を採用するが、すでに業界的にはその次のトランジスタ構造としてCFETの実用化に向けた動きが進められており、同社ブースでも模型を使ったCFETの紹介なども行っている。

チップレットにも注力

また、プロセスの微細化の物理限界に伴って、高性能化のけん引役として期待される先端パッケージング分野についてもさまざまな研究成果の紹介が行われている。

例えばチップレット分野に向けてはシリコンブリッジ直接接合技術を用いた「Direct-bonded Silicon Bridge Technology(DBHi)」やシリコンブリッジ内蔵インターポーザーを用いた「Molded Fan-out Interposer Technology(MFIT)」。このほか、光電融合分野として、独自のポリマー導波路技術を用いたCo-packaged Optics(CPO)パッケージであったり、3D実装に向けた放熱ソリューションなども紹介している。

放熱ソリューションは、同社が「両面放熱技術」と呼ぶもので、半導体のパッケージ表面だけでなく、パッケージ基板側からも冷やせるようにすることで熱問題を解決しようというもの。半導体パッケージング技術などに関する世界最大級の国際学会「The 2025 IEEE 75th Electronic Components and Technology Conference」(ECTC 2025)で発表されたばかりの、パッケージ基板にグラファイトシートを埋め込み、水平方向に熱を逃そうという最新の取り組みについての紹介も行われていた。

量子コンピュータやアナログコンピューティングにも注力

このほか、同社ブースでは同社の量子コンピュータの最新世代である「IBM Quantum System Two」のモックや、AI処理向けハードウェアユニット「AIU」の取り組みの一環としての12nmプロセスベースのニューロモーフィックチップ「AIU NorthPole」、14nmプロセスベースでBEOLにPCM(相変化メモリ)を埋め込み、アナログ・インメモリ・コンピューティングとして、PCMのコンダクタンスにニューラルネットワーク(NN)の重みづけを局所的に保存し、積和演算を行うことでメモリ内で演算処理を実現し、低消費電力と高性能演算の両立を実現する「AIU analog」なども紹介されていた。