Rapidusは4月1日、新エネルギー・産業技術総合開発機構(NEDO)より「ポスト5G情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発(委託)」における「日米連携に基づく2nm世代半導体の集積化技術と短TAT 製造技術の研究開発」、ならびに「2nm世代半導体のチップレット・パッケージング設計・製造技術開発」の2025年度計画および予算が承認されたことを発表した。

2nmプロセス量産の前段となるパイロットラインの立ち上げを開始

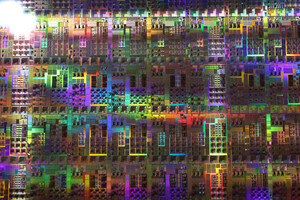

日米連携に基づく2nm世代半導体の集積化技術と短TAT 製造技術の研究開発は、2022年11月に次世代半導体研究開発プロジェクトとして採択されたもので、同プロジェクトの委託先であるRapidusは、半導体前工程拠点「IIM」の建設を北海道千歳市にて進めてきた。

今回の2025年度計画および予算の承認は、プロジェクトの技術パートナーであるIBMにエンジニアを派遣して2nmプロセス技術の習得を進めてきたほか、EUV露光装置をはじめとする各種の先端プロセス対応半導体製造装置のIIMへの設置、クリーンルームの稼働開始などといった2024年度の目標を達成したとの判断を踏まえてなされたもの。承認された前工程向けの予算は上限6755億円で、主な計画としては、第1工場であるIIM-1への短TAT生産システムに必要な装置、搬送システム、生産管理システムの開発およびパイロットラインへの導入と、そのパイロットラインの4月1日からの立ち上げとそれに伴う300mmウェハを用いた2nm GAAトランジスタの試作開発の本格化、ならびに先行顧客向けにPDK(Process Design Kit)のバージョン0.5を2026年3月(2025年度末)までにリリースする計画で、これらをもとに顧客によるプロトタイピングの実施に向けた環境整備を進めていくことを予定しているとする。

-

小池氏が製造速度向上の鍵の1つと語った搬送系。通常はウェハを収めるFront-Opening Unified Pod(FOUP)をOverhead Hoist Transport(OHT)が収納して、設置してある搬送レールに従ったルートで次の工程に運ぶが、IIM-1では決まったレールを敷くのではなく、グリッド形式とすることで、自由自在な工程間搬送を可能とし、生産効率(レール方式だと、ストッカーや待機所を用意して、次の工程の装置に空きが出るまで待機する必要が生じる場合がある)を高めることができるという

PDKは、ファウンドリがファブレスなどの顧客に提供するプロセスをもとにした回路設計に必要な情報をまとめたキットで、すでに2024年度までにバージョン0.2が先行顧客などに提供済みとするが、機能拡充や精度、使い勝手などの向上を図っていく必要がある。

-

回路が大規模化した近年の半導体設計は複数の段階に分かれており、徐々に実際の回路パターンに落とし込んでいく必要があるが、ファウンドリ各社の製造プロセスは特性などが異なっているため、それぞれに応じたPDKを使って、それぞれのプロセスに適した形で設計する必要がある

また、同社代表取締役社長 兼 CEOの小池淳義氏は、パイロットラインの立ち上げに関して、「4月1日よりウェハを実際に流すための条件出しが可能になった」とし、「今のところ、早ければ7月中旬から下旬ころにある程度の(ウェハの性能の)確認ができるとみている」とする。詳細は語らなかったが、おそらく4月からの3か月ほどで各装置の初期立ち上げを行い、7月の段階でTEG(Test Element Group)と呼ばれる設計や製造時の不良などの評価・解析を行うテストチップの製造を実施。枚葉式製造の特長と同社の掲げる素早い製造に向けて、その各工程におけるパラメータのフィードフォワード/フィードバックによるチューニングを量産にも適用することを目指した取り組みも並行して進めていくのではないかと思われる。

同社の量産を開始するスケジュールは2027年度を計画しているが、半導体の前工程は少なくともウェハを投入して回路が形成されて出てくるまで数か月、長いものだと一年近くかかることを考えると、量産開始時からある程度の歩留まりを達成しようとすれば、意外と残された時間は少ない(長く見積もっても3年ほど)。同社はこれまでも、1枚ずつウェハを処理する枚葉式によって、圧倒的なデータ量を得られることとなり、それを活用することでパラメータの最適化などを図って、高い歩留まりや性能を実現すると公言してきており、パイロットラインの時点から、実際にウェハを流しながらそうした手法を取り入れることを考えれば、この3か月ほどという立ち上げの時間軸で済ませられる可能性がある。

後工程研究施設に製造装置の搬入を開始

一方の後工程(チップレット)については2024年3月に採択されたプロジェクト。2024年度中に基本プロセスフローの決定および製造装置の選定が完了したほか、IIMに隣接するセイコーエプソン千歳事業所内に半導体後工程の研究開発拠点「Rapidus Chiplet Solutions(RCS)」の設置を決定し、2024年10月より稼働準備に向けた作業が進められている。

承認された後工程向けの予算は上限1270億円で、その主な用途は、4月からのRCSへの製造装置の搬入を稼働開始と、それに伴う2nm世代の半導体を含む3次元(2.xD、3D)パッケージ製造技術の開発による要素プロセス技術の確立が挙げられる。具体的には600mm角のパネルを活用した有機絶縁膜RDL(Redistribution Layer)インタポーザの開発や3Dパッケージ技術、量産化技術の検証などが含まれている。また、アプリケーションごとに最適な高効率/高性能チップレットパッケージの設計およびテスト技術の開発も挙げられている。こちらは、主に最新の後工程技術に対応したADK(Assembly Design Kit)の構築推進や品質管理手法としてのKGD(Known Good Die)の選別フローの開発などを進めていくとしている。

ちなみに、これらの先端パッケージング開発はグローバル連携で進められ、エプソンとのRCSでの協業や技術研究組合 最先端半導体技術センター(LSTC)、産業技術総合研究所(産総研)、東京大学(東大)などといった日本での取り組みに加え、前工程でも連携するIBMのほか、独FraunhoferとはRDLインターポーザの開発で協力、シンガポールのA*STAR(シンガポール科学技術研究庁)の研究機関であるInstitute of Microelectronics(IME)とダイをウェハ上に接続するDie-to-Wafer(D2W)やチップレット技術の調査で協力する。

小池氏は、「前工程は米アルバニーでのIBMの基礎研究を経て、日本に技術を持ってくる。後工程はエプソンのRCSを活用して研究開発を進めていき、将来的にIIMで前工程と後工程を合わせて提供していくことで、付加価値の高いファウンドリサービスを提供していきたい」とし、歩留まりや信頼性の確保が今後の課題となるが、一歩一歩検証を進めて、2027年度の量産開始につなげていきたいとしていた。