ルネサス エレクトロニクスは11月14日、同社の車載向けSoC「R-Carシリーズ」として初の第5世代品(R-Car Gen5)となるハイエンドSoC「R-Car X5H」を発表した。

同製品は「Software Defined Vehicle(SDV)/Software Defined Mobility(SDM)」時代に求められる自動運転(AD)/ADAS機能、IVI、車外との通信を行うためのゲートウェイや各種ECUとの通信制御などといった機能を担うビークルコンピューティングにセントラルコンピュータとして対応することを目的に開発された第5世代R-Carプラットフォームの最上位品に位置づけられるもの。TSMCの車載向け3nmプロセス(N3A)を採用し、アプリケーション処理用にArm Cortex-A720AE CPUを32コアを搭載することで1000k DMIPS以上の性能を提供するほか、リアルタイム処理向けにCortex-R52 CPUを6コア(ロックステップ対応)も搭載、60k DMIPS以上の性能を提供することで外付けマイコン無しでASIL-Dに対応することが可能だという。

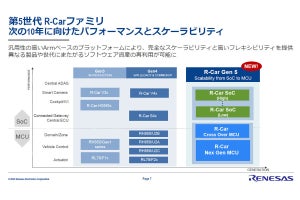

車載半導体市場の現状。SDVに向けて1つのアーキテクチャでエントリクラスからラグジュアリクラスまでソフトウェアの共通利用なども含めて対応したいというニーズが自動車メーカー側から強まっている。R-Car Gen5はそうしたニーズを踏まえてすべてArmアーキテクチャベースで統一して開発される (資料提供:ルネサス。以下すべてのスライド同様)

プロセスの微細化に伴い、従来の5nmプロセス製品比で消費電力を30~35%低減したとのことで、チップ全体のターゲット消費電力は上の方の2桁Wとするなど、高い電力効率を活用することで強制冷却だけで利用できるようにするとしているほか、ソフトウェアによる細かな電力制御も含めて消費電力の平準化なども進められる見通しで、そうした取り組みを通じて、システム全体のコスト低減と電気自動車(EV)の航続距離延長の両立を図ることを可能にしていくとする。

また、同じモノリシックダイの上に、最大400TOPS(Sparse)のAIアクセラレータ(NPU)ならびに最大4TFLOPSのGPUも搭載(いずれもパートナーのIPを採用)しているほか、UCIe(Universal Chiplet Interconnect Express)にも準拠しており、顧客の要望に応じてチップレット形式でNPUやGPUをさらに追加して1チップ化することもでき、より高度なAI処理やグラフィック処理に対応できるとする。このチップレットでの提供については、ルネサスが顧客から請け負ってパッケージ化する場合と、顧客が自分たちでOSATなどに委託してパッケージする場合の両方が想定されており、同社ではAPIの提供も行うことで、外部のUCIe対応チップレットとの組み合わせも可能としており、場合によっては別テクノロジーで製造されたAFE(Analog Front End)なども接続できるなど、柔軟性を顧客に提供するとしている。

R-Car X5Hは基本的にはモノリシックダイで構成されるが、顧客の要望に応じて機能拡張を実現するためにUCIeに準拠しており、チップレットとしてパッケージ内で複数ダイを接続して演算性能の向上などを図ることができる仕様になっている。いわゆるインターポーザを介して、さまざまな機能を持つチップレットを組み合わせて作るPCやサーバ向け半導体とは若干、チップレットの意味合いが異なっていることに注意が必要である。同社も参加している車載向けチップレット開発を目指すASRAはおそらく後者の考えに近いものと思われる(この製品のコンセプトは1年以上前から考案されているので、ASRAの動きの前から開発が進められていた)

さらに、車載システム開発で課題となるセキュリティ&セーフティへの対応として、Cortex-Aに搭載されるTrustZoneではなく、独自開発のハードウェアベースのパーティション技術を採用。これにより複数の異なる安全レベルを要求されるソフトウェアへの干渉をなくすことを可能(Freedom from Interference:FFI)とした。これにより、ブレーキなど高い安全レベルが求められる機能と、そこまで高い安全レベルが求められないIVIの処理などを同じX5H上で処理しつつも、安全かつ完全に分離することができるようになり、高い安全性が求められる機能には冗長化した独立ドメインを割り当てるなど、各ドメインに独自のCPUコア、メモリ、インタフェースを持たせることで、他のドメインのハードウェアやソフトウェアに故障が発生した場合でも影響を受けずに安全に機能させることを可能にしたとする。加えて、ワークロードの優先順位を見極めてリアルタイムに処理リソースを割り当てるQoS(Quality of Service)管理機能も備えているともする。

-

機能ブロック図でいうところの「Safety/FFI system」の部分がこのミクスド・クリティカリティを担う機能を持つ。この制御には搭載されているArm Cortex-AならびにCortex-Rとは別のCPUコアが担うという

なお、同製品は2025年上期に一部の自動車顧客向けにサンプル出荷を開始し、2027年下期に量産を開始する予定としているほか、同社ではR-Car Gen5はエントリクラスからラグジュアリクラスまであらゆるクルマに対応するプラットフォームとしていることから、機能シュリンク版のエントリ向けSoCの提供や、より機能を限定したArmマイコンなども提供していく予定としており、中でもボディならびにシャシー向け32ビットArmマイコンとして、セキュリティを強化した新たな車載制御用マイコンを2025年第1四半期にもサンプル出荷させる計画としている。